ESD失效分析

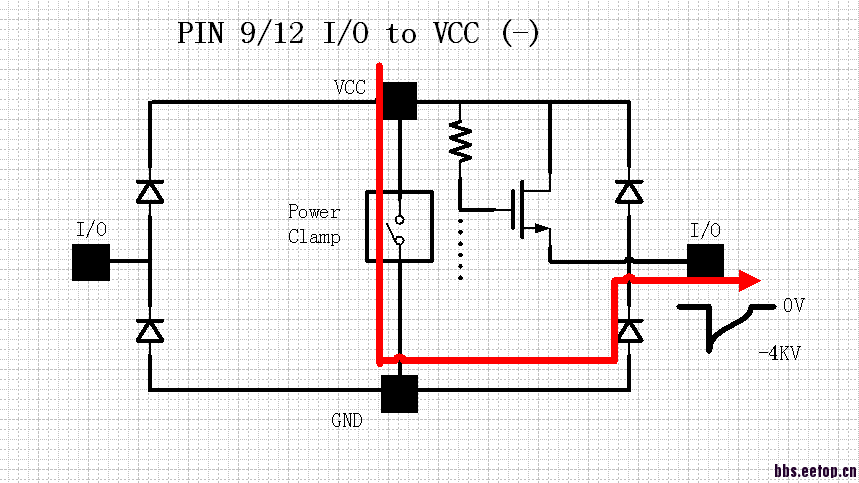

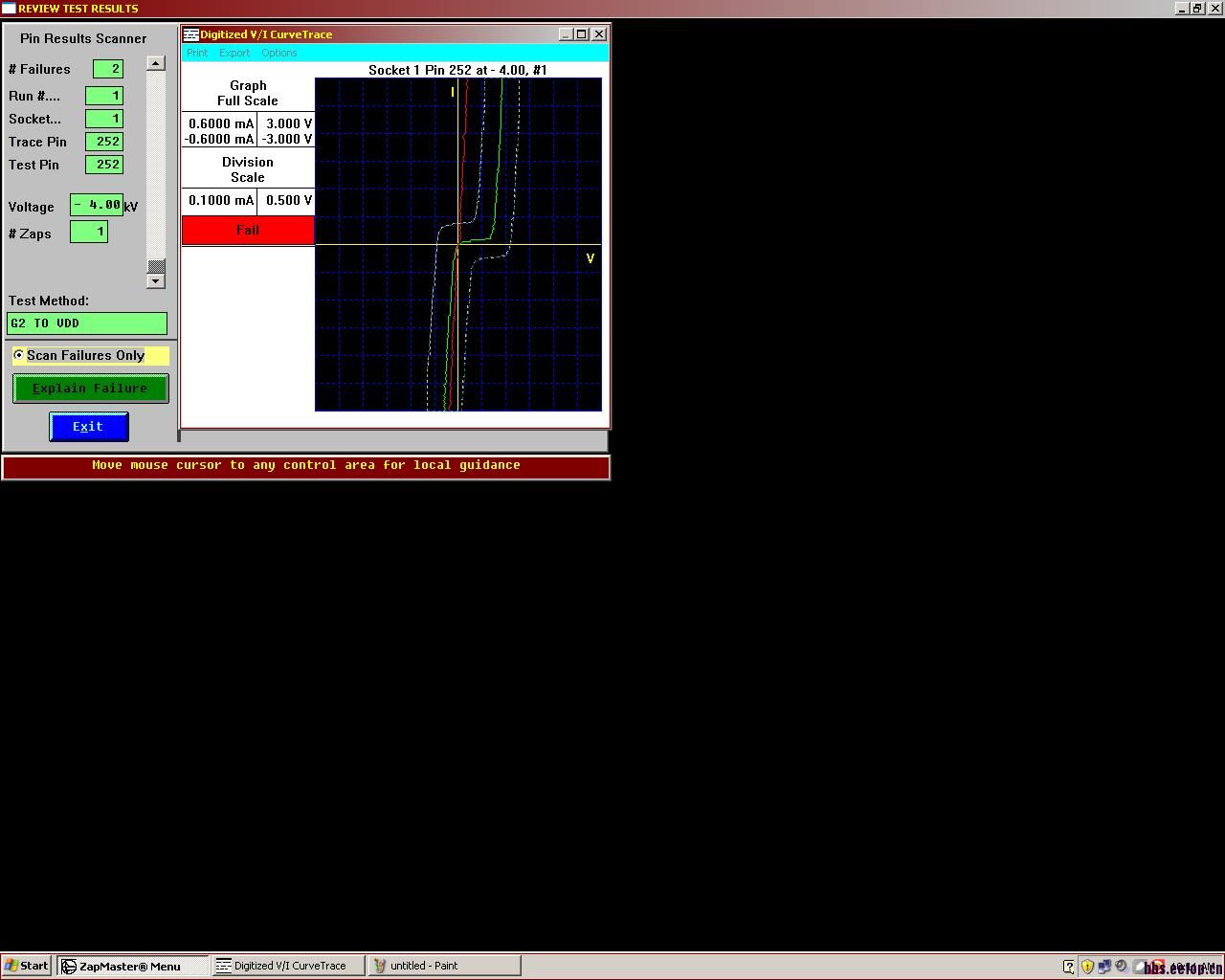

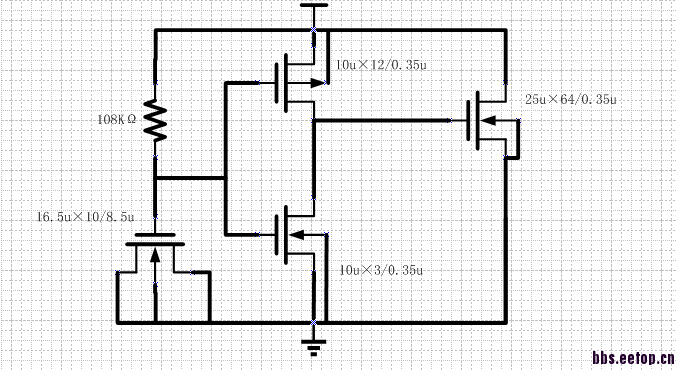

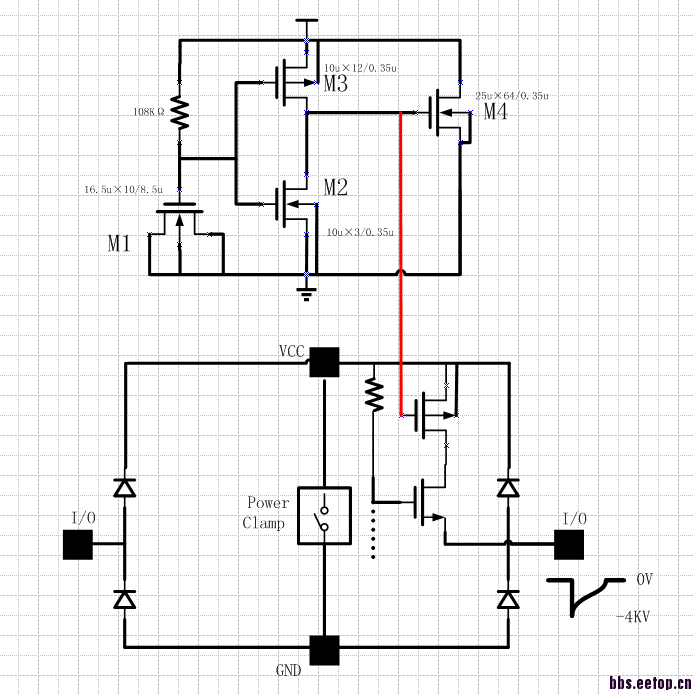

IO输出电路是Floating source的, ESD之后该IO损坏。IV曲线如红色下图中红色所示,绿色是未做ESD之前的IV曲线,明显看出正电压时电流偏大,除了Diode外,还有哪些地方可能损坏,如何改进。

[img]file:///C:\Users\Administrator\AppData\Roaming\Tencent\Users\22701347\QQ\WinTemp\RichOle\%989HR1K`E{S_B~`ZW~GZ@T.jpg[/img]

请问小编你的图中的软件的名字是什么?

从图中来看,IO对VCC打-,最容易的通路是NMOS,而不是你用红线画出来的预期路线,所以损坏点很可能在NMOS处,话说打坏后开盖应该能看到损坏点。

ESD电流有3个可能的路径:1、通过IO处对地二极管正向turn on到gnd ring,然后再通过Power clamp击穿snapback或者trigger,到power ring泄放

2、内部nmos snapback或者breakdown,与nmos sub连接也有一定关系

3、IO处对 power的二极管breakdown

1是你预期的路径,但esd能否从这个通路走,取决与powerclamp的设计是否合理,是否足够块trigger,还包括PAD的位置,GNDring和Power Ring的寄生res

如果ESD电流从2、3通路走,你整个ESD的设计就失效了,从2走的可能性更大。

如果要优化改善,首先要确认powerclamp是否起作用,另外就是减小PAD到powerclamp的路径的res,如果chip很大,要考虑muti的powerclamp,在PAD附近增加一组powerclamp

更重要的是要保证内部nmos本身的robust,具体涉及到device的size(是否足够到self protect),layout的是否io rule,应用中是否可以加电阻等等

对于3路径,一般如果按照fab esd design guideline ,应该不大会出现

大牛分析的很全面,我也怀疑大量电流经过2通道泄放了,导致NMOS过流损坏。

本芯片面积不大(1mm*1mm),有两个Power clamp,HBM测试其它项都通过了

(IO to IO ±, ALL to GND ±, ALL to VCC+),只有该类型的两个IO to VCC- 没有通过。

IO的NMOS是 2V的Native Vth, 本芯片工作在3.3V电压下,所以相比3V NMOS,该Native NMOS

更容易损坏,NMOS尺寸L=0.35um,W=10*19um。你指的足够self protect如何衡量?

我觉得改进方法一是在NMOS漏极加一个电阻(如下图红色虚框所示),限制大电流流过NMOS。

还有其它改进建议么?谢谢。

1.限制大电流不会影响这个脚的驱动能力么?

2.NMOS的bulk接哪?

3.话说I/O to I/O都能过,有没有想想I/O to PIN9/12是怎么过的?

谢谢提出疑问。

1. 放个比较小的电阻,比如10欧姆,只是限制ESD时discharge的超大电流。

该IO的驱动电流最大20mA左右,所以最大压降200mV,不会影响工作点,也不会限制驱动能力。

2. NMOS的bulk与芯片的地直接相连。

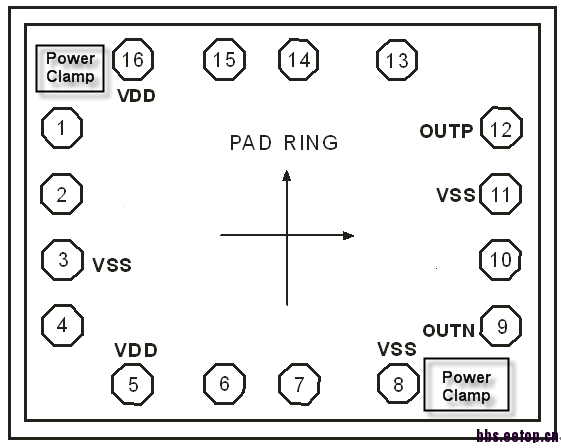

3.确实,IO to IO比 IO to VCC更苛刻。 唯一可以理解的是有9个IO分布在芯片四周,而VCC只有两个。

所以IO to IO 时的电荷泄放能力也不差。

注明: 本芯片管脚图如下,9个IO, 两个VCC,三个GND。Power Clamp位于两个角上。

19u*10的size显然是做不到selfprotection的 你这个应用如果ESD性能要求比较高,建议D和S端都加电阻。一般电阻也不是你想的这种加法。

一般都是单个finger加,比如10个device D,S分开layout,然后每个上面加10欧

这样均匀性更好,总的电阻也才只有1欧

4#的分析很到位!

"NMOS的bulk与芯片的地直接相连" High Risk! 其实是个潜在的ESD 放电通路 取决于该MOSFET 的Break Down voltage 如果你也是低压MOSFET 可能这个管子挂掉的几率爆高

看不懂

这个办法好,并联既能限制大电流通过NMOS,又不电流降低驱动能力。

唯一的牺牲是稍微增加了NMOS的寄生电容(从finger改为multi)。

是的,3.3V 电源,但是1.8V的NMOS,本身就会有breakdown的问题。

本工艺是0.18 CMOS Nwell工艺,NMOS的bulk只能接地,如果想降低该风险,有何建议呢?

可参考10#楼建议 这种做法很长用 就是比较费点size 串的电阻的大小 Power Clamp是什么结构的 GCNMOS, GGNMOS,。 clamped 电压多少伏。

需要详细知道一些工艺的参数去算 还是有一定risk

想请教个问题,为什一定要用此电路 “IO的NMOS是 2V的Native Vth”

designer不能想个办法避免掉吗 用NMOS 有什么好处吗 作为上拉? 还是其他的用途

电路又不能关段 又不能防漏电…… VCC tracking?

觉得本身这样的想法就有点怪怪的

3.3V 工艺用1.8V NMOS 抗? 可靠性问题!

常规来说这个1.8V break down voltage可能会远高于3.3V, 但是现在由于衬底的连接 NMOS break down voltage trigger point 会大大降低

另外这个NMOS不是一直通的吗 因为其是native mosfet 其一直就是个ESD 通路

为什么不能用PMOS 或者上边串连一个PMOS。

这样可以大大降低风险

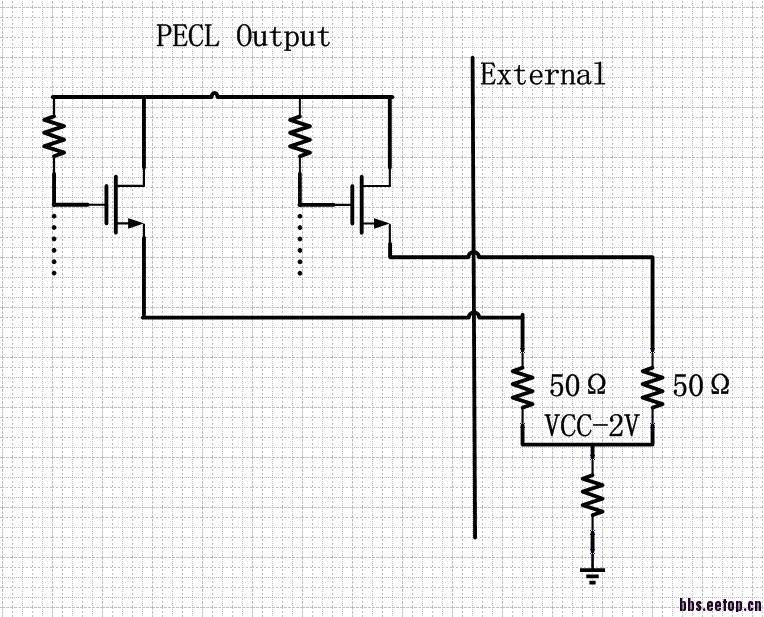

关于这个输出IO的应用说明如下:

差分输出LVPECL接口,外接电阻到地。根据LVPECL的电平要求,

输出共模VCC-1.3V,单端电流14mA左右,本芯片工作在1Gbps速率。

CMOS 018工艺能够满足要求的设计就只能采用Native FET了,而且要采用1.8V

的FET满足速率要求。

Power clamp 见下图,所有器件都是3V FET。

NAT NMOS 上不可以串接一个3.3V PMOS PMOS gate接在GCNMOS INVTER后面处 即NMOS Gate位置?

你的意思是指下图所示吧:在PowerClamp放电器件,关断Native NMOS的放电通道,起到保护作用。

实际中有没有靠PowerClamp来控制电路的?有无这方面的实际经验,还请指导。

交流使人进步!

you can do the simulation and check NAT NMOS drain voltage value...

Sure

for ESD event, you can do it, but need to do one simulation to check it

大牛,关于Breakdown Voltage(BV),在PDK的哪里可以得到数据?

1.8V的NMOS, VDS VGS的BV一般是多少? VSB VDB呢?

BV中VGS是不是最小?

我们一般保证VGS<2V VDS<2V, VSB VDB就很少关注。不知道是否正确?

通过交流取的进步是不错的, 希望国内在Esd 方面能有象sofics 这样的专业Esd ip 公司产生, 大家一起努力。

是的,交流促使共同进步。希望大家深挖,多提携疑问和建议。

power clamp是什么?

电源与地之间的钳位电路,电源上接收到高脉冲电压时,为电源和地之间提供电荷泄放通道。

VERY GOOD

难得的高技术含量贴子。

BV的数据一般可以在PCM文档里找到。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。