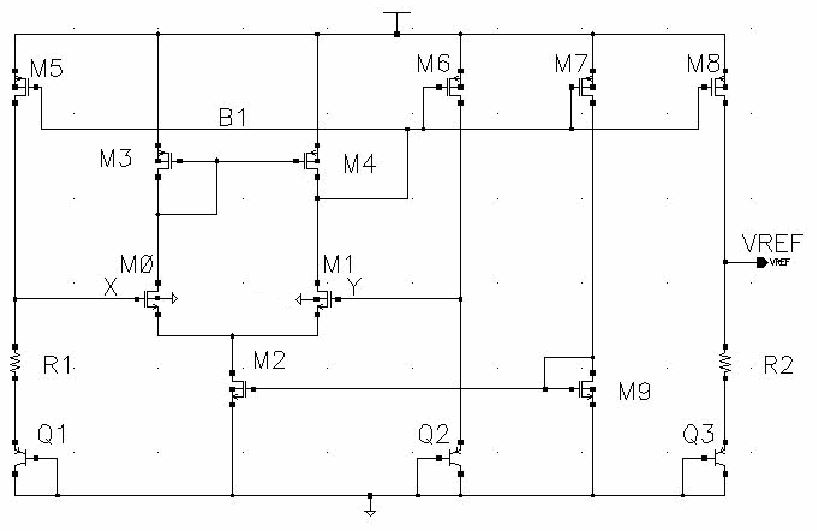

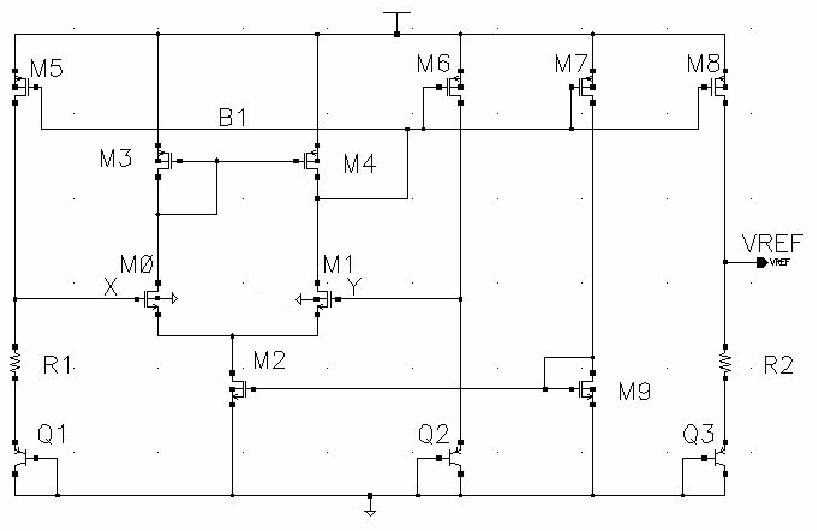

问一个带隙基准的运放问题(尾电流源不饱和怎么办)

如图是何乐年的书中的一个简单带隙基准,有一疑问 ,运放输入端被钳定后 ,电压大概在700mv左右,就是一个三极管的Vbe那么大,在0.35um工艺下,一个MOS管的阈值电压就是650-660mv,这样留给尾电流源的M2漏极只有40--50mv ,结果就是这个电压值小于60——70mv的Vdsat,使尾电流源处于线性区。还有一种可能是尾电流源饱和而输入管在亚阈值区。

请问我的分析是否哪里有问题? 如果没有那这个电路怎么才能调通呢? 使用一个线性区的尾电流源 ,对运放乃至整个带隙基准有什么影响?

是有这个问题,但是影响不是很大,M1M0的开启电压可以设置在大约600mV左右,M1的W/L略大,M2的Vds有100mV也可以了

当然这个OPA 的增益不会太大,也只是够用,效果不会很好。

你可以仿一下ss

把M0,M1,M2,M9的W/L搞大或者把M2换成电阻

最好的解决方法是把运放输入换成P管

input pair最好换成pmos,别忘了把start up电路加上。

带隙里的运放一般是p管输入。

为什么纠结用PMOS?如果考虑匹配和增益,噪声等因素,NMOS具有一定的优势。此结构采用NMOS管,为了保证输入电压摆幅,通常选用低阈值或者本征NMOS即可。小于一个VBE。这样对工艺是有一定要求的。切莫使用耗尽管。

用pmos省钱

为了你的良率好,请改用P input

两位小编说的都一定有道理。这里如果用图中的single stage ndiff pair opamp做bandgap 的clamp amplifier,最好选用lvt的管子做差分对输入,否则常规nmos做差分对输入很难保证在宽温度范围内有很好的clamp effect.尤其是在高温。如果工艺限制只能用normal vth device,建议选用单级pmos diff pair input folded cascode amplfier.国外公司一般这两种都用过。从成本考虑建议用第二种。

8楼说“为什么纠结使用PMOS管?如果考虑匹配、噪声,NMOS有一定的优势。”这句话是不是错了?应该是PMOS管的噪声比NMOS管小吧?求解答?还有为什么PMOS省钱?不是应该NMOS面积小,且省钱么?

NMOS主要是匹配和增益有优势,噪声没有。

低阈值或者本征NMOS需要加工艺层、加mask,所以花钱多。analog IC不要太纠结面积。

建议输入对管换成PMOS管。NMOS和PMOS各有优劣,从良率的角度,该运放用PMOS管更好一些。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。