请教input buffer

源跟随器的电流变化了百分之几?正常电流是多大?

多少的工艺?

下面是电流源,为什么说源随器的电流变化很大那,没做过adc,只是比较好奇哈!

大概变化了3%,65的工艺,这方面的资料太少了,李福乐说bipolar片内集成buf,cmos片外加,但我不知道原因是啥

问题是如果是片外加buf,带上封装电感仿真会发现,对200m的adc,输入信号来不及在一个周期内建立,不知道这个问题在工程上是如何解决的?

说电流源的变化也可以,差不多,怎么办?

确保都在饱和区,还有65nm工艺输出电阻不大,可以适当加大电流源的输出电阻

3%也差不多了,你正常工作电流多少?

输入共模怎么管?

source follower能有多好,而且高频下会随current source impedance下降而变差

一般还会有背栅效应,大swing case下 的harmonic

方便把你的结构大概说说吗?

他应该不会说的,或者给你私信。论坛很多人都这样。怕抢饭碗

呵呵,没什么好的结构

要么片外单独用颗buffer

要么到高压做input buffer

要么放弃高阻输入,做个几Kohm的输入阻抗

不过已经有几年不做这东西了

再说buffer要做到高频还保持很低的harmonic本来就是件困难的事情

让输入级驱动,哈哈

呵呵,还是这样最省事

可是如果考虑封装电感的话,我在外部加理想源都不行,传到芯片内部已经有很大的ring了,这样的话岂不是没法测了呢?

这和加不加buffer又有什么关系呢?

不好意思没表达清楚,如果不加内部buffer,采样开关的切换使输入阻抗不是恒定的,加上封装电感的话,即使片外给理想信号,传到片内会因为阻抗的高速切换引起ring,进而影响线性度,而内部加了buf,这个阻抗就比较恒定了,这是我的理解,请问对吗

sample就是个settle过程,bonding wire 也就几nH,算一下impedance

如果你所担心 sample switch couple 出来的那点charge,那也不是问题

片外本来就要做50ohm termination,片内在做一点resistor termination

请问是在采样开关前面串联一个50ohm电阻吗?

并联50ohm

实验了一下,貌似串联电阻效果更好啊,我迷茫了,

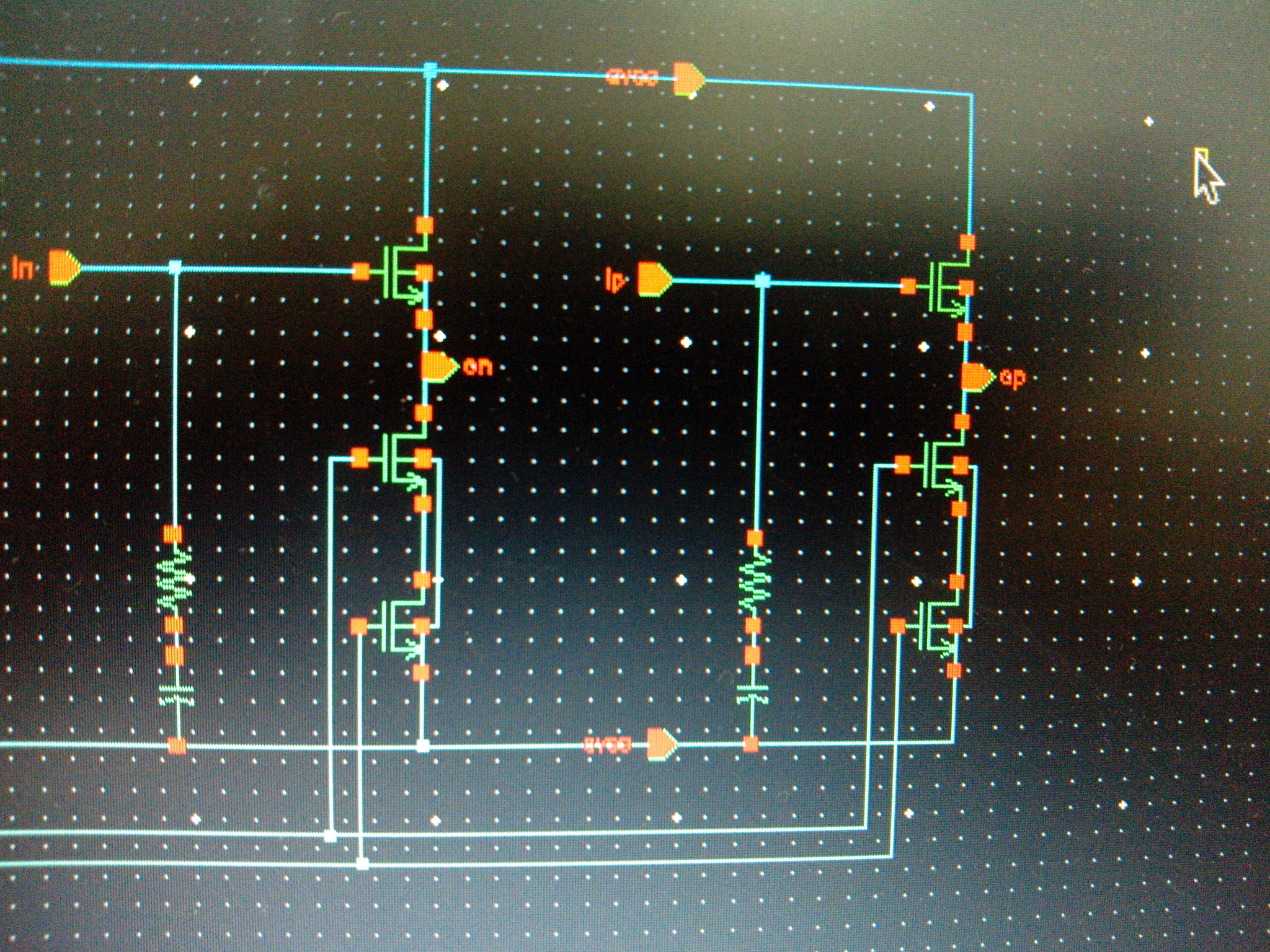

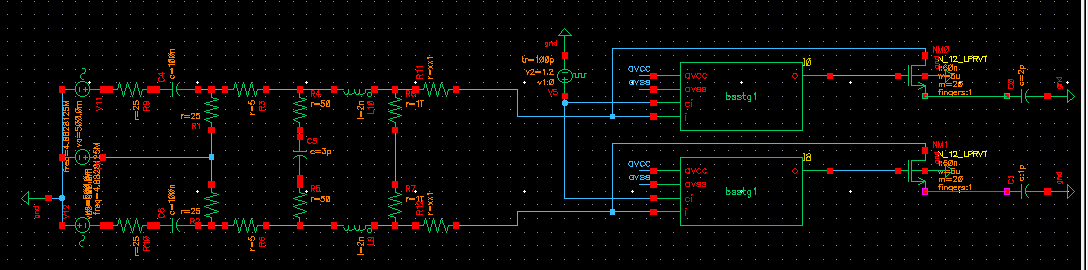

这是我的电路,有一些器件只是测试效果用的

本人最近也在做ADC输入buffer,请问各位有什么好的参考资料吗?

小编测过经过封装模型后信号的SFDR吗

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:反型层的电子来自哪里?

下一篇:charge pump产生负压必需要DNW吗