求助一个带隙基准电路

没有大神会么?

求大神粗现。

把CDL网表附上吧 需要仿真琢磨

单看电路的话很难看出什么东西来是吧?好吧,那我单仿以后给出你要的文件,之前仿真的时候结果是A点和B点电压是相等的。就是不知道为什么,Q3和Q4看着像各自组成单端输人的简单放大器。

顶顶,不要沉啊

小编是我电微院的吧,学号这么熟悉,这种BGR好像很少见

呵呵 能够搭出如此精简电路之人……

是在校学生搭出来的吗 还是哪家芯片里的电路

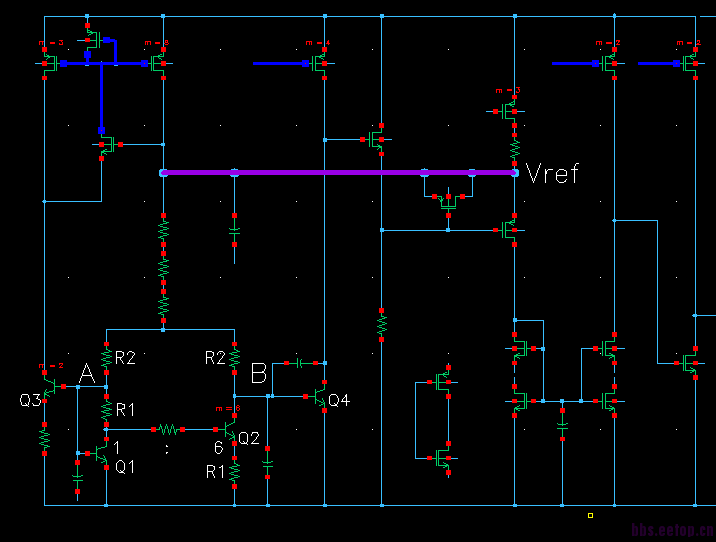

右邊電路部份是啟動電路外加判定,基準電路是否OK,左邊是電路主核心

具體看你可以拆成幾部份看

最左邊你可以看成是個表示電路產生I1=Delta Vbe(Q1/Q3)/R BIAS 电流 中间部分是一个产生电流为I2=Delta Vbe(Q1/Q2)/(2*R1) , 最左邊上面NMOS 流過的DC 電流 即是兩者之差 即In=I1-I2 如果电流镜比例为1:1

BGR 数值测试VBEQ1+ I2*(R2+Rx)

整个电路则是 一個負反饋 你可以看成3个小环 即bias 电路(local feedback)+ local feedback (Q2+R2)+ loca feedback (Q4+Source Follower + VREF) 具体如何断loop有多种断法 取决于自己怎么看着舒服 怎么去断,每个人或许有不同的断法

顶起学习中

感谢你的回答,但是我有几点疑问,先把你的回复重述如下

右邊電路部份是啟動電路外加判定,基準電路是否OK,左邊是電路主核心

具體看你可以拆成幾部份看

最左邊你可以看成是個表示電路產生I1=Delta Vbe(Q1/Q3)/R BIAS 电流 中间部分是一个产生电流为I2=Delta Vbe(Q1/Q2)/(2*R1) , 最左邊上面NMOS 流過的DC 電流 即是兩者之差 即In=I1-I2 如果电流镜比例为1:1

BGR 数值测试VBEQ1+ I2*(R2+Rx)

整个电路则是 一個負反饋 你可以看成3个小环 即bias 电路(local feedback)+ local feedback (Q2+R2)+ loca feedback (Q4+Source Follower + VREF) 具体如何断loop有多种断法 取决于自己怎么看着舒服 怎么去断,每个人或许有不同的断法

我想问的是I1=Delta Vbe(Q1/Q3)/R 这个成立的条件是Q1和Q3的集电极电压要相等的吧?(或者说流过Q1和Q3的电流相等)这里怎么保证它是相等的?

另外,中间I2=Delta Vbe(Q1/Q2)/(2*R1)的电流应该也有条件才能成立吧?比如说A点和B电压嵌位相等什么的。

期待你的解答,谢谢。这是凌特的片子里面的芯片,学生一般会搭比较常规的电路吧

西电微院的,我是学号党

Q3 和Q4应该是保证A和B相等的运放输入端,但是运放的负载不是很清晰,电路再整理整理。

这个电路和这个很像

http://bbs.eetop.cn/thread-482081-1-1.html

二极管Q3,Q4作为放大器的两个输入端,Q4上面的p管(称作P1)把最左边Q3的电流复制过来,在Q4和P1之间对Q4和Q3电流作差,即为放大器的输出;然后又经过共源放大器连到了Vref,最右边是一个负反馈,完成A,B节点电压的钳位(P1)。

大神不要这个表情,好不好啦。

你说的Q3 Q4作为运放的输入端,Q3的m值是2,且加了个源级负反馈电阻,还可以看成是差分输入?

大神,我看到你说这是一个最最简单的电路,书上有说明?我怎么觉得这样的带隙结构很少见啊?这里A,B点怎么嵌位?上楼有人说了相关的理解,我也提出了我的疑问,你给看看吧。万分感激

对,我看了那个贴子,是很像,但是回帖的人也比较少,也没有解答清楚

负反馈为了稳定电路,不会改变差分结构吧,至于具体参数,那得是后来调试后在改进了,个人认为电路是这么工作的。

主要是感觉差分运放应该是一个对称的结构,特别是输入管,一边采用负反馈电阻,另一个也应该采用吧,不然运放的失调怎么考虑呢?这也是我个人观点,最好能有相关书将这样的电路结构是最好不过了

顶一个。

再顶一顶,大神出现吧。

求大神。

顶一顶。大神出现

1.先说下从哪儿弄来的电路,能保证准确性么

2.如此奇葩的BGR,到底是出于什么目的。

凌特公司的带隙电路,能保证电路的准确性吧。

vref上面的pmos的gate接哪里?

另外最好把尺寸显示出来。

属于基本结构的改进,但不知道该基准的特点,方便透露产品型号嘛?根据其对Veference的spec认识优点

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:Tx frequency offset

下一篇:12b ADC IP 问题