电容共模反馈全差分运放碰到的问题,做过的童鞋帮帮忙,多谢

录入:edatop.com 阅读:

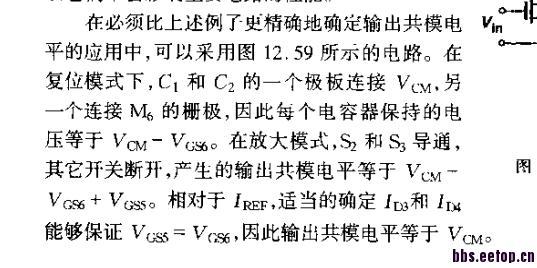

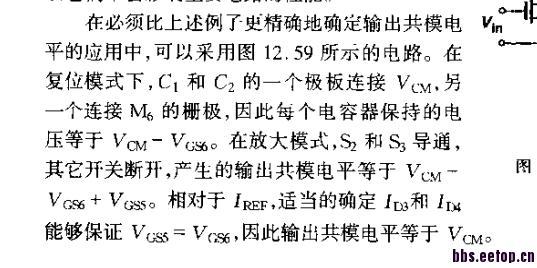

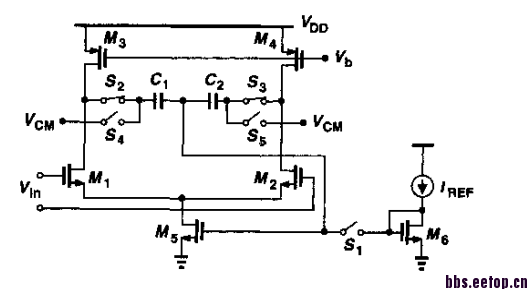

最近在做一个双端运放的时候,用到了拉扎维书上的方法

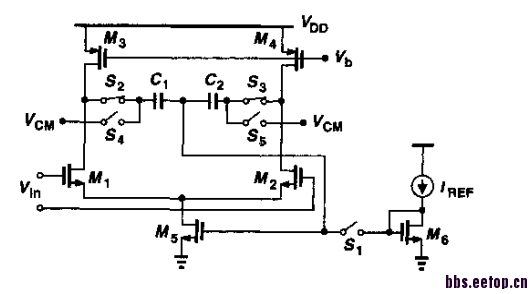

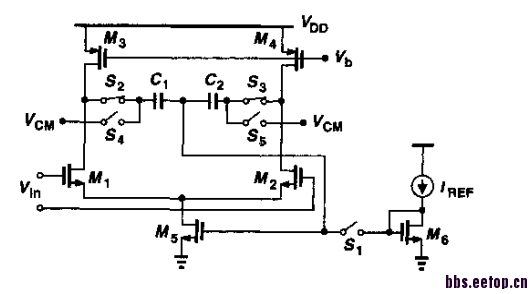

。但是我在做的过程中,采样模式的时候不能保持在VCM,放大模式的时候可以很好的保持。如图:

。但是我在做的过程中,采样模式的时候不能保持在VCM,放大模式的时候可以很好的保持。如图:

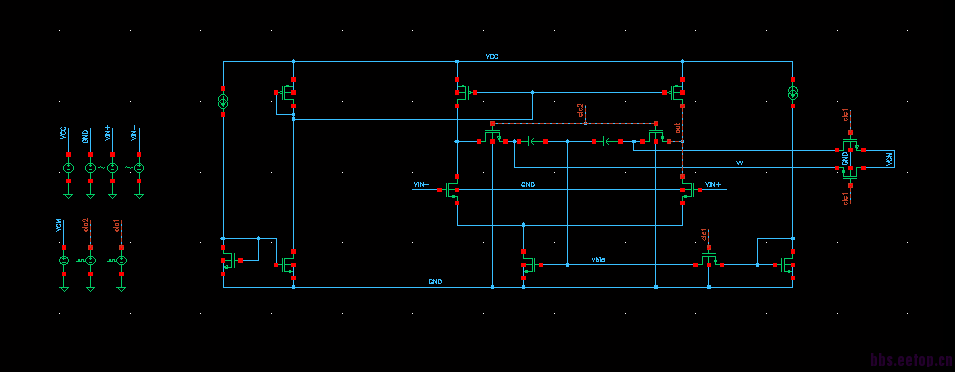

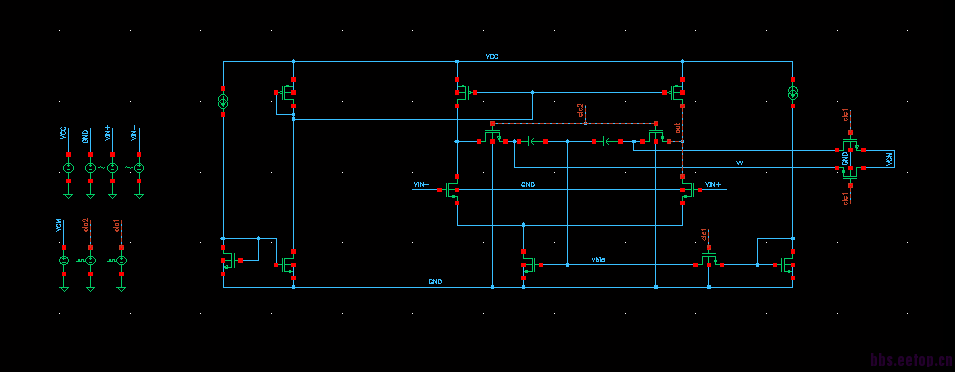

。clc2控制S2和S3,即控制放大模式,这个时候可以看出来输出端是在我想要的电压1,但是clc1高电平的时候,即在采样模式的时候输出电压却在1.5v。仿真显示Vgs5和Vgs6在每个时钟都是基本相等的。

。clc2控制S2和S3,即控制放大模式,这个时候可以看出来输出端是在我想要的电压1,但是clc1高电平的时候,即在采样模式的时候输出电压却在1.5v。仿真显示Vgs5和Vgs6在每个时钟都是基本相等的。

我把这个电路的复位时钟即clc1隔很长的时间来一次高电平(考虑电流的泄流效应),那电路基本处在放大模式,这个时候仿真可以。但是不知道实际上是怎么处理的。

希望大家耐心看下,给下指导,谢谢

。但是我在做的过程中,采样模式的时候不能保持在VCM,放大模式的时候可以很好的保持。如图:

。但是我在做的过程中,采样模式的时候不能保持在VCM,放大模式的时候可以很好的保持。如图:

。clc2控制S2和S3,即控制放大模式,这个时候可以看出来输出端是在我想要的电压1,但是clc1高电平的时候,即在采样模式的时候输出电压却在1.5v。仿真显示Vgs5和Vgs6在每个时钟都是基本相等的。

。clc2控制S2和S3,即控制放大模式,这个时候可以看出来输出端是在我想要的电压1,但是clc1高电平的时候,即在采样模式的时候输出电压却在1.5v。仿真显示Vgs5和Vgs6在每个时钟都是基本相等的。我把这个电路的复位时钟即clc1隔很长的时间来一次高电平(考虑电流的泄流效应),那电路基本处在放大模式,这个时候仿真可以。但是不知道实际上是怎么处理的。

希望大家耐心看下,给下指导,谢谢

采样模式的共模输出电压可以是1.5V,此时s3断开的,out和电容没连接,如果不存在任何失配的话,应该是VDD-Vds4

可是我想这个电路应该得到比较稳定的静态工作电压VCM吧,如果采样模式不能在VCM的话,是不是就像我上面说的,只需要过段时间采样一次就行了,不用那种不停的对称方波采样

不需要把,采样过程由开关电容完成就行了,只要在保持状态运放的工作点是对的就行了,如果你要在任何时候运放的共模输出都是一样的,那你就不要用这种开关电容做共模反馈

是不是说这种结构就是用它的放大模式?

这种结构是用在采样保持电路里的,不是说只用保持模式。

好像少了点什么

少了什么?

最近也在做流水线ADC,遇到了不少的问题,看一看,学习一下!呵呵。

。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:最近仿真了一个5阶3位的连续时间sigma delta模数转换器,snr不高,请指教分析原因?

下一篇:运放setting time与那几个参数相关,如何设计呢