运放输出问题

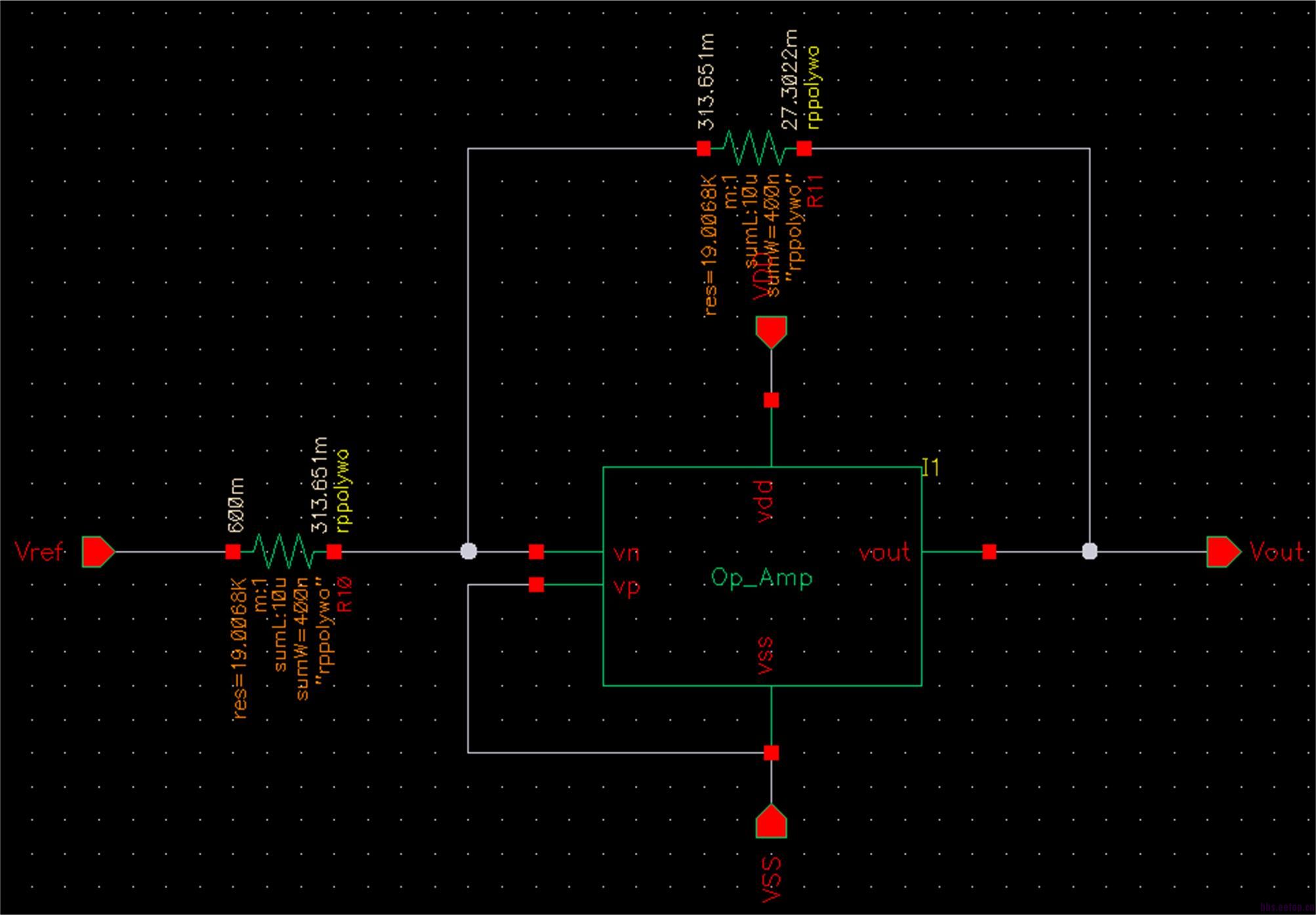

补充一下,VDD=1.2V, VSS=0V,Vref=0.6V, 两个R相同

(600+27)/2 = 313.5

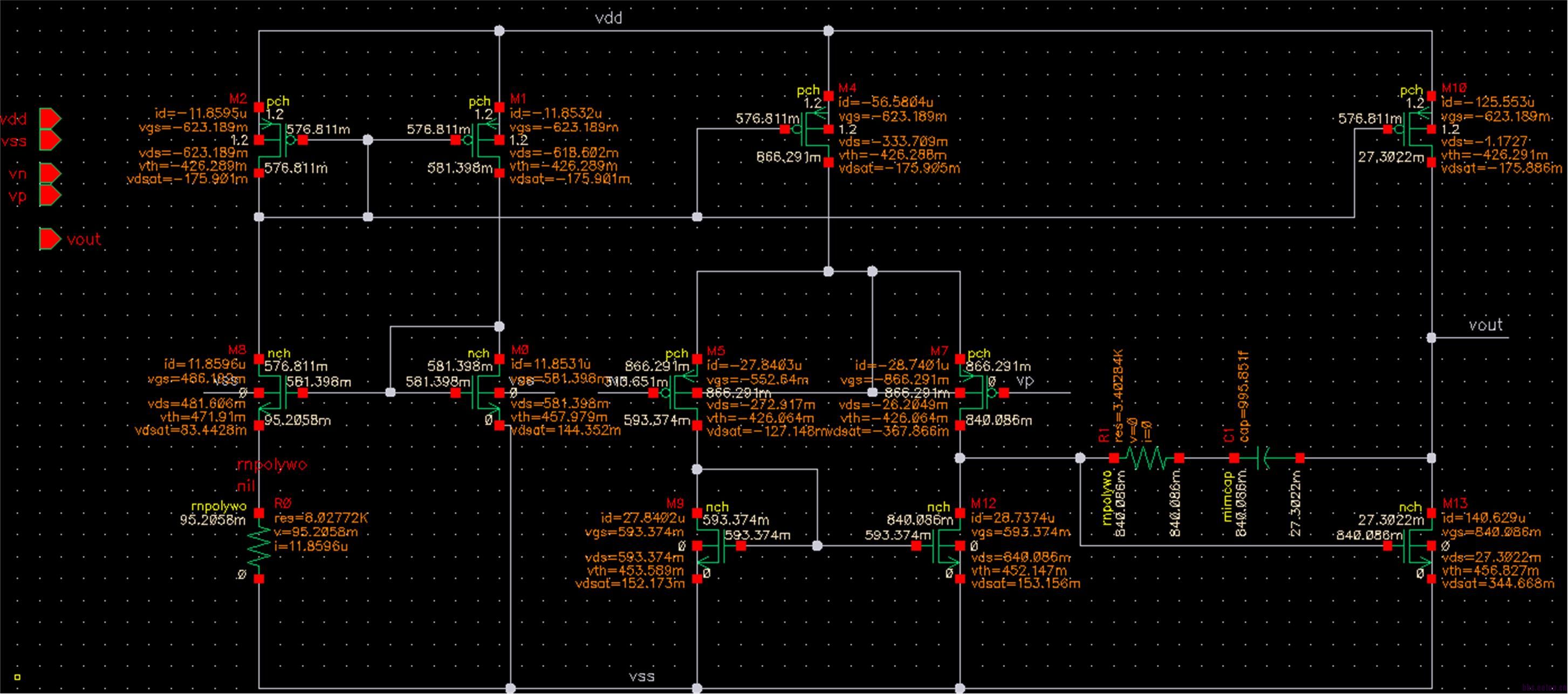

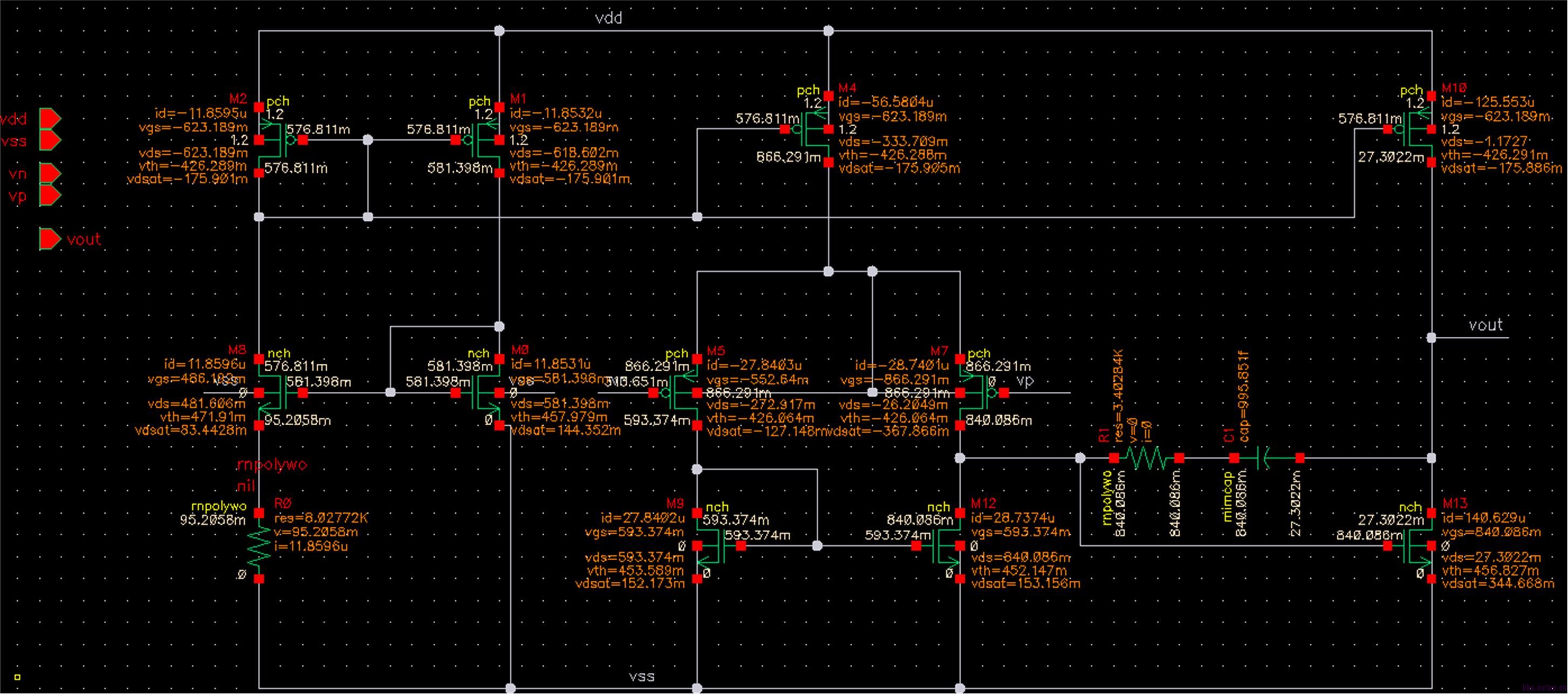

你看下Vp管子的工作状态

运放的结构什么样的,输出级可以驱动电阻负载吗?就电阻之后,内部的静态工作点你看看

接vss满足运放的共模输入范围吗?

直观感觉是运放内部管子没有工作在饱和区

您看看

您看看

当前内部结构

是有两个管子没有工作在饱和区。如果工作在饱和区,那就会出现Vn=0V左右?

这个运放的输出级是个高阻输出,适合驱动容性负载,输出驱动电阻,输出阻抗肯定很小了。我想你在输出级加个Buffer试试。我没软件不能调试了直接告诉你,你试试吧

小编好像对运放输入端接地理解错了,那是交流地,直流电平不一定是0.

如果Vp直流电平没有限制为0的话,建议修改

小编这么接是电流放大型,如果运放工作的话,其输出电压为-600mv,而此时输出管子是永远无法进入饱和区,运放的工作是不正常的。

小编,你没有直流偏置。运算放大器是在直流点附近工作的。也就是说在交流分析中,OPamp是线性器件。你看一下你设计的M7管子,作为一个输入管子没有bias到饱和区是不对的。

check您的M10, 看是否因為size問題而使其進入TRIODE Region. 如果是的話, 加大其m, 使得電流輸出足夠後, 即可使Vout提升至0.6V. 如果不想改OPAMP的話, 將R由19K改為190K也是個解法, 不過noise會變大. 一切就看您的需求了.

赞同14楼的意见。小编还是先看一下运放的输入输出范围吧

输出阻抗19K,增益大于1么?你把两个电阻换成19M以上的就ok了。

Vp应该设置为共模电平吧,而不是0吧

1. 运放的VIP也应该是共模电平,

2.所谓的反相放大器说的是交流小信号,,不是直流偏置点

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:我下的TSMC的工艺库为什么不能安装?

下一篇:电压模DCDC大占空比不稳定的问题