诚心求助MDAC

运放仿真AC,DC, 瞬态应该都没问题,开关是理想开关,时序应该也没问题,但是输出不对,请问可能是什么原因。诚心求问,其他不多说了,直接上图

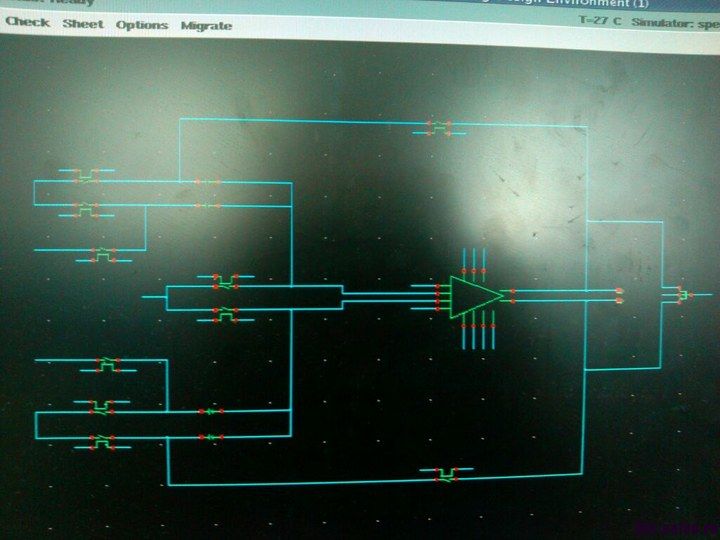

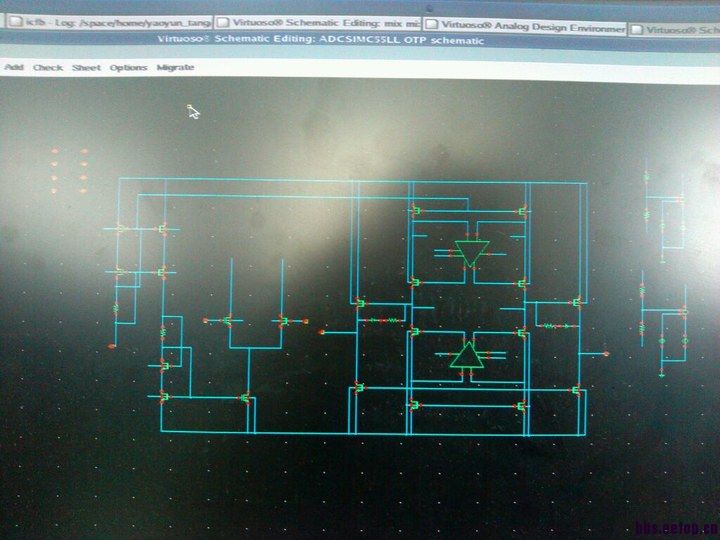

运放仿真AC,DC, 瞬态应该都没问题,开关是理想开关,时序应该也没问题,但是输出不对,请问可能是什么原因。诚心求问,其他不多说了,直接上图第一张图是MDAC的整体

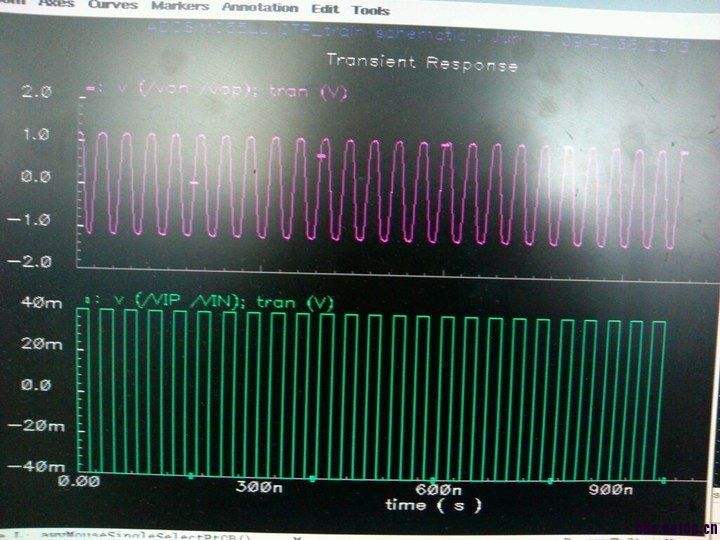

第二张是运放的瞬态,绿色输入,红色输出;

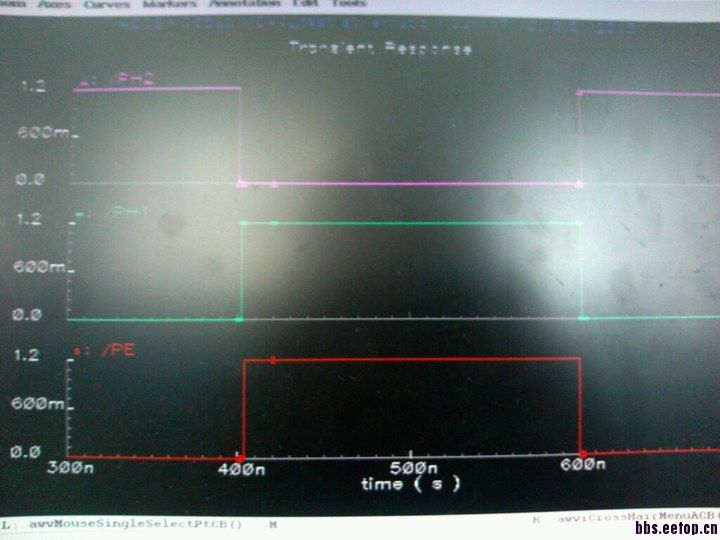

第三张是开关的时序PH1是采样开关,PH2是放大开关,PE是共模开关;

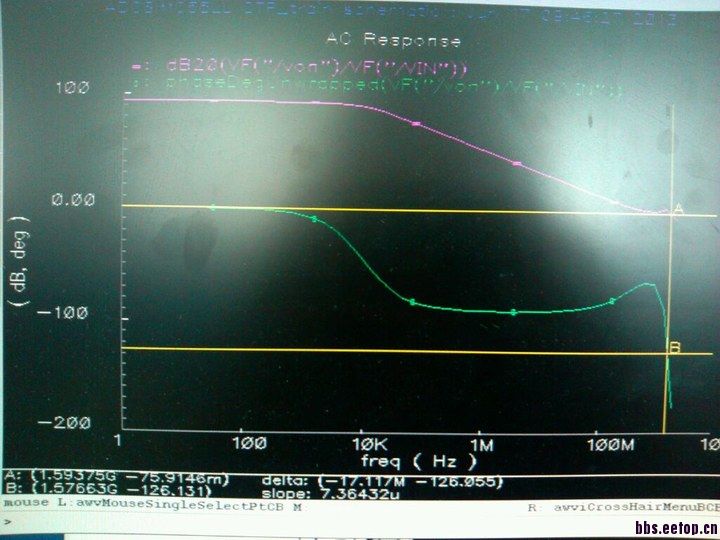

第四张是运放AC,增益90db,带宽800M

两个疑问哈。

1. 为什么MDAC输出貌似没有reset的过程,始终都是在-1和1之间翻转呢?

2. 从你OTA的AC来看,你这个运放不能用

那个不是MDAC的输出,是运放的瞬态波形。能详细说说AC有什么问题吗?

你的运放时不是用的ahujia频率补偿?

运放的结构是这样的,应该是米勒补偿吧

哦,米勒补偿啊,

折叠+gain boost增益才90db?

恩,是55nm的工艺,电源电压才1.2V,第一次做MDAC,不知道要注意什么?

小尺寸的工艺我不熟。只是凑个热闹。

主要是想问一下,做MDAC的时候对运放有什么要求没有?

MDAC我更不熟。嘿嘿。

自己顶下,不要沉了

问题基本解决了,理想开关不行的,换成栅压自举开关,好多了

耀云哥,你的运放结构共模反馈电流各工艺角下差距不大吗?

认识的啊,你是哪个?我没仿过其他corener。

chenmaokui,这个结构第二级共模反馈电流太大,不太容易控制

共模反馈用一个就行了吧

嗯,第一级加共模反馈

1. 你OP的bode plot 0dB點之後翹起來 可能有補償問題 跑一下setp response, fully differential OP bode plot 要看different mode & common mode

2.第1,2級MDAC 做好一點 後面可以鬆一點

3.Capacitor mismatch是pipeline ADC 的較大error source, 最好做multi-bit MDAC 加上digital calibration

Capacitor靠近OP input 接capacirot top plate, sampling MOS (leading clock) 用NMOS, 接buttom plate 的用transmission gate, 第一級的MDAC 可考慮用boost gate sampling.

建議前面幾級做multi-bit MDAC with digital calibration (or capacitor average technique)

用two stage OP 比較耗電 但是signal swing 較大 可以用在前幾級

後面幾級可以用 folded cascode OP

太感谢了,豁然开朗啊

小汤啊,你居然做ADC去了。神奇的娃啊你这运放明显不能用,基础要紧~

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。