同步BUCK下管驱动诡异

录入:edatop.com 阅读:

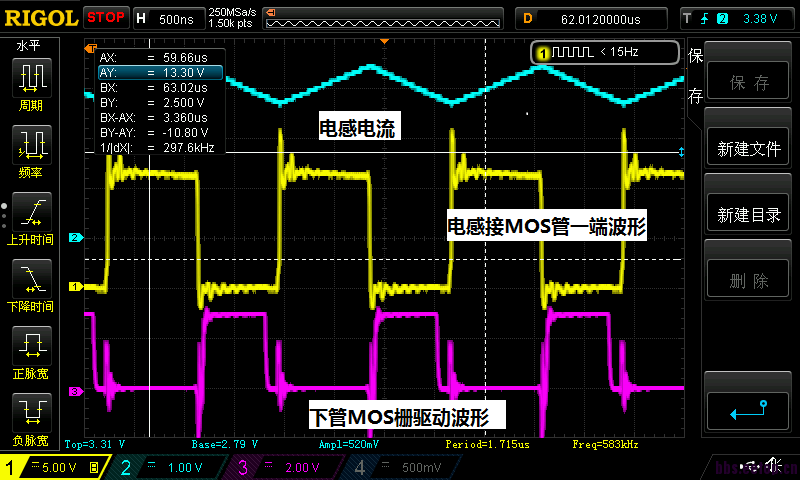

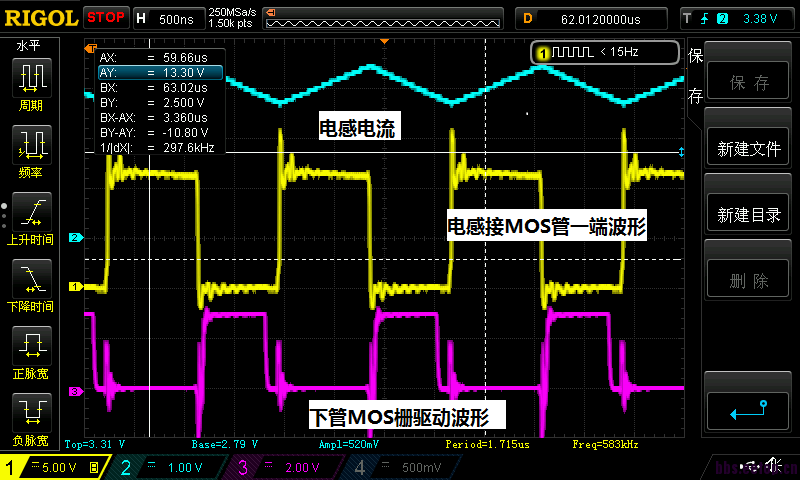

如题,测试了一个同步BUCK IC,IC提供下管的驱动电压,设计值应该是0~4.5V的电平变化,可是现在被外置MOS管弄得高电平只有3V。而且下管打开时,电感接上、下NMOS管一端的波形不断的震荡,导致效率非常低。请问有人知道这个是什么原因么?MOS管是60V/5A的管子。

上管开的太快,下管毛刺过大,可能短时都打开效率低。可以把上管驱动接一电阻

感觉上管关和下管开之间的Dead time太小吧,测下来有多少

开pmos时,lx(sw)电压升高,通过下管nmos栅漏寄生电容,耦合到nmos的gate,使nmos在这个瞬间导通。一般高压大电流的DCDC,这个是非常要注意的,你现在效率低还好,没烧就不错了。设计时注意sw的上升速度,还有nmos的驱动级的下拉能力一定要非常强。也就是pmos慢点开(分段),nmos快关。同时大电流高压时,很多节点的电压,电流变化非常快,通过寄生的L,C会产生很多noise(EMI设计注意,降低这些电压电流的变化率,当然也牺牲效率了。)

你这个没烧估计是因为片外的功率管吧。你可以在外置的nmos的gate对地加个电容,这个电容约10倍Cgd_nmos寄生电容。看看改善没。

恩,我先试试。

测试出来差不多20~30nS的样子,不知道这个参数怎么样?

恩,谢谢指导,后续我会调整这些参数。 现在还有一个疑惑就是什么东西把芯片驱动下管电路的高电平给拉低了,比正常值小了1V左右,而且始终不能恢复。

恩,都是片外的功率管

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。