CDR的jitter仿真

录入:edatop.com 阅读:

请问怎么仿真得到CDR恢复出来的数据和时钟的rms jitter?如何仿真整个CDR环路输出时钟的phase noise?

cadence计算器里的eyediagram得到的眼图怎么看出jitter信息啊?

cadence计算器里的eyediagram得到的眼图怎么看出jitter信息啊?

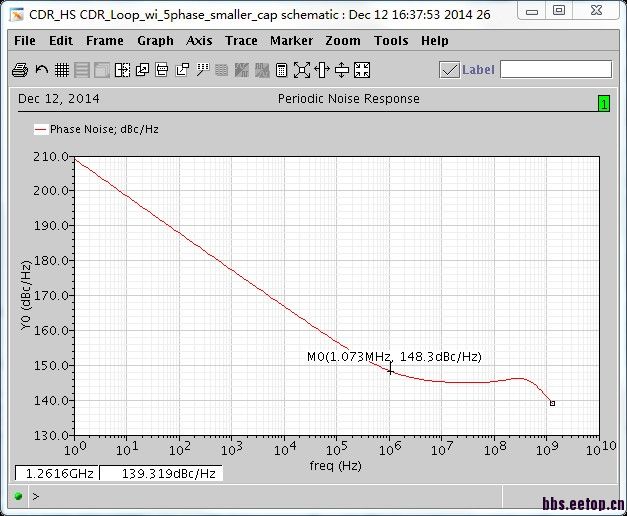

我用pss+pnoise仿真得到的CDR的phase noise曲线 如下,不知道是不是设置上有问题?

不知道为什么phase noise的纵轴值是正的,跟仿VCO的情况不一样啊

眼图根本看不了抖动,tran仿真不包含器件噪声

嗯,之前也听人说过,那仿真眼图可以看什么呢?之前是没办法,是因为pss+pnoise不收敛,改设置后虽然收敛了,但phase noise曲线如上,还是有问题?

仿真眼图只可以看看由杂散引起的确定性抖动,PLL整体的输出相位噪声你都可以在cadence里面仿出来?是不是CDR分频比为1所以好收敛,我觉得最好是仿真出每一个局部模块的相位噪声,然后在MATLAB里面去拟合

嗯,是这样的情况,我的CDR分频比为1,但不清楚整个环路跑psss+pnoise的设置和单个模块跑时的区别?

和分频器一样

good article

内容学习

如果采用Bang Bang结构,可以通过眼图看tracking jitter的大小,不包含器件噪声,只是系统的抖动。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:各位模拟大师,运放输入端作用,用在锁相环PLL,消除电荷共享的单位增益缓冲器

下一篇:dcdc输出小电流时输出电压震荡