PLL后仿无法锁定的问题

很可能是divider不工作了。

感觉原因就是你的VCO后仿跑不到125M,分频器跑不到这个频滤是很难想象的,实际上你能看vctrl,那么你也应该能看vco的输出波形,判断削顶后vco的频率到没到要的频率,再看分频器能不能分频

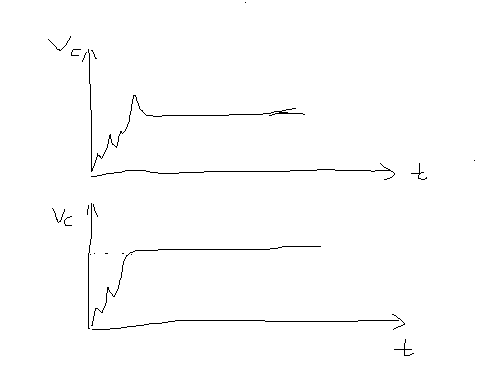

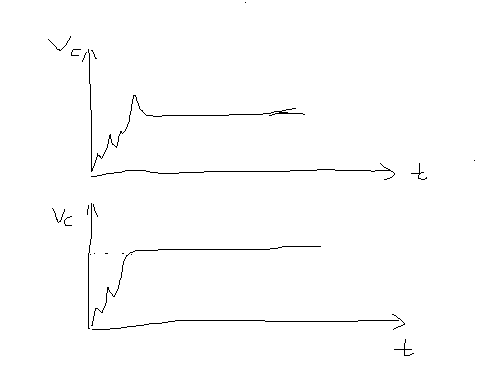

下面的图是在ss85下的Vc形状,在正常的锁定过程中,Vc过冲之后会再下降以达到振荡频率对应的电压;在ss85仿真中,没有过冲,Vc上升至接近电源电压就变平坦,此时对应的cko频率只有110M左右;VCO单仿时,在Vc电压等于1.5v时,输出频率就达到124.7MHz; 在其它条件下,过冲发生时,cko频率可达到130MHz以上;在tt45条件下的仿真也是没有问题的;感觉是在ss85,Vc过冲时,VCO频率上不去了,应该是这时导致的问题;问了下别人,说VCO的设计一般会留1.2倍或者1.5倍的裕量,我调试VCO的时候基本上是在ss85下刚刚覆盖124MHz,可能频率范围留的不够的问题;

谢谢你的指点~

应该不是divider的问题,因为frequency不是很高,可能是我VCO设计裕量不够 谢谢你的指点~

您好,我是一个菜鸟,想学PLL,您能帮我推荐一些关于PLL设计的书或者资料吗?O(∩_∩)O谢谢

VCO的频率随控制电压变化非单调变化,是问题所在吧

恩,也可以这么说,从VCO的仿真数据来看,在vctrl=0.5~1.4范围内,输出信号的频率是随Vctrl线性增加的,大于1.4后,频率-VC的斜率变为0,VCO输出信号频率不再增大;感觉Vctrl选到1.4v,已经有点偏高了,应该把Kvco再增大一些;

这个就是问题所在

还有一个问题想请教下哈:

VCO的前仿数据和后仿数据基本上是一样的,环路仿真时,我的前仿在ss85下锁定和cko的频率也都是没有问题的,如果说VCO的设计裕度不够,是不是在前仿真的时候就应该反应出来?

谢谢~

这个问题作一个VCO 后仿 (corner)不就证实了么

不是divider的问题,很可能就是VCO的问题了,SS是频率偏低,所以VCTRL会一直向上漂要锁到相应的频率。一般会用AFC之类的来克服corner的偏差。

“我调试VCO的时候基本上是在ss85下刚刚覆盖124MHz “就是没有考虑过冲的问题。

域度太低。

LZ的PLL VCO工作在有些CORNER达不到所希望工作的频率,其实即使VCO勉强可以达到工作频率,也还需要看VCO此时增益还有多大,环路还是否有足够增益,有没有足够相位裕度等等。

请问LZ你的后仿使用什么软件仿真的?怎么查看phase noise的?

因为我做的是给数字用的clock,所以没有考虑phase noise,用hspice 跑的后仿;PLL的phase noise需要建模型吧,虽然做过这个,但一直没有在实际的设计中使用过,单block的phase noise都是用spectre跑的;

那单模块的PN后仿的时候怎么在结果里查看?正常schematic调出ADE进行仿真里可以directplot-main里有PSS和PNOISE的函数可以使用,但是我直接用spectre +input.scs跑后仿网表,跑完并没有保存可以计算PN的参数。请问你是怎么查看后仿PN的或者怎么仿真后仿的?最近就这纠结了好久了,谢谢啊

最近在做一个PLL的后仿,在Corner=ss,temp=85,LV=1.7V的仿真条件下,在仿真最高频率124MHz时,环路无法锁定,VC上升到接近电源电压,然后就很平,完全不是PLL应有的环路仿真特性,VCO的后仿可run到125MHz;然后降低一级分频系数,仿真120MHz时,锁定及最终输出频率是没有问题的,124MHz在其它PVT下也没有问题;请有经验的大侠指导下这是哪个地方的影响呢?怎么来改进呢?

很可能是divider不工作了。

感觉原因就是你的VCO后仿跑不到125M,分频器跑不到这个频滤是很难想象的,实际上你能看vctrl,那么你也应该能看vco的输出波形,判断削顶后vco的频率到没到要的频率,再看分频器能不能分频

下面的图是在ss85下的Vc形状,在正常的锁定过程中,Vc过冲之后会再下降以达到振荡频率对应的电压;在ss85仿真中,没有过冲,Vc上升至接近电源电压就变平坦,此时对应的cko频率只有110M左右;VCO单仿时,在Vc电压等于1.5v时,输出频率就达到124.7MHz; 在其它条件下,过冲发生时,cko频率可达到130MHz以上;在tt45条件下的仿真也是没有问题的;感觉是在ss85,Vc过冲时,VCO频率上不去了,应该是这时导致的问题;问了下别人,说VCO的设计一般会留1.2倍或者1.5倍的裕量,我调试VCO的时候基本上是在ss85下刚刚覆盖124MHz,可能频率范围留的不够的问题;

谢谢你的指点~

应该不是divider的问题,因为frequency不是很高,可能是我VCO设计裕量不够 谢谢你的指点~

您好,我是一个菜鸟,想学PLL,您能帮我推荐一些关于PLL设计的书或者资料吗?O(∩_∩)O谢谢

VCO的频率随控制电压变化非单调变化,是问题所在吧

恩,也可以这么说,从VCO的仿真数据来看,在vctrl=0.5~1.4范围内,输出信号的频率是随Vctrl线性增加的,大于1.4后,频率-VC的斜率变为0,VCO输出信号频率不再增大;感觉Vctrl选到1.4v,已经有点偏高了,应该把Kvco再增大一些;

这个就是问题所在

还有一个问题想请教下哈:

VCO的前仿数据和后仿数据基本上是一样的,环路仿真时,我的前仿在ss85下锁定和cko的频率也都是没有问题的,如果说VCO的设计裕度不够,是不是在前仿真的时候就应该反应出来?

谢谢~

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。