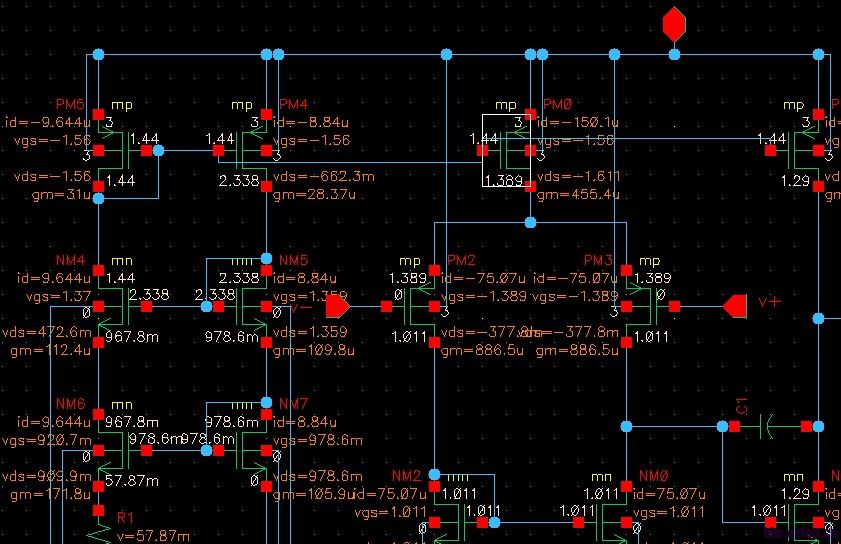

理论计算和实际仿真数据差距有点大,不知道是否是在合理范围?

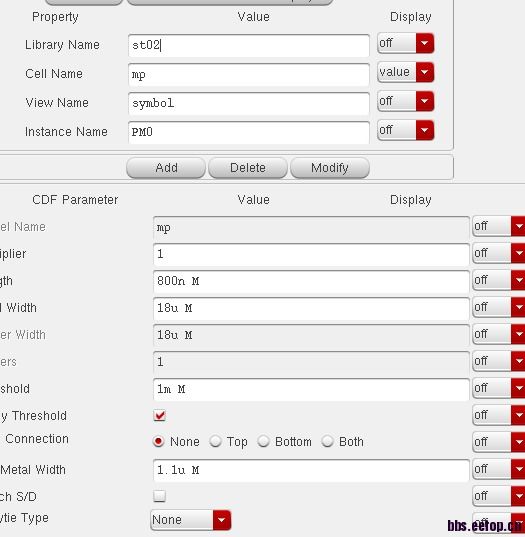

一个电流10u,可另一个达到了150u,这也差距太大了。算上沟调也差的太多了吧。

一个电流10u,可另一个达到了150u,这也差距太大了。算上沟调也差的太多了吧。

PM0应该是12(1.5/0.8),误差会小一些

一般偏置电流为运放电流20%左右,二者越接近,误差越小

ps:左边的偏置需要启动电路;PM5产生的偏置电压太小,导致输入共模范围很小

谢谢,你说的很清楚,不过偏置电流为输入管电流20%是不是在误差和功率消耗之间做的一个比较好的折衷?

我很想笑...请别这么计算,你被中国的教育制度毒害了...课本上就是逗你玩,你别当真,唯一的解决方法是找个牛人,看你的福分了,他要肯教你,你就会发现,书上的MOS偏置计算就是扯淡!除了sansen讲了点实话。

靠,你还挺有钱的,看来这个坛子里钱不等于经验啊!

相差不多12倍变成了15倍对吧,相差了。基本就是手算的模型和方针模型差距比较大了。手算只是提供一个设计的思考。对于变化趋势的一个解释。可以用 gm/i的那种模拟结合计算的方法设计。再有你的输入对管没有在饱和区。

同学,这类偏差以后你还会发现很多。

这就是现实呀~呵呵

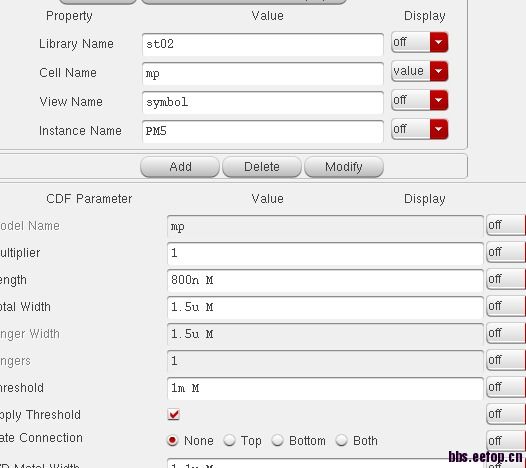

倍乘电流,不要倍乘W,要多用几个管子,用multiplier。要知道即便这样,vds的影响也是不可忽略的,就算仿真好了,做出来也还是会有偏差。模拟的经验是需要慢慢积累的,多学多做,加油。

谢谢指点,但是你说没牛人指点就不行,我是不太相信的,而且我非常相信理论指导实践这句话,只有课本上知识学好了才有举一反三

vds=300mv,我的过驱动电压才0.12V,所以是在饱和区,也就是说是在合理范围咯,只不过是因为模型不太好的原因,导致差距偏大?

谢谢,你说的对,我还是同学。0.0

小编 请教一下 为什么我手算一个简单的共源晶体管的饱和电流是仿真的大概两倍?我以为我忘记除2了,可是我明明已经除以把Id前面的1/2带上了啊····L设置为最小长度的10倍,这时候沟道长度调制应该已经很小了吧·····可是还是这么大差距··

VDS的值呢?将漏压调大一点应该会改善

1.注意model中的有效w和l

2.一些model,w不同,vth也会变化

以上

居然是个坟

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:新手求助:关于调零电阻与相位补偿问题、输出摆幅

下一篇:请问这是什么器件?