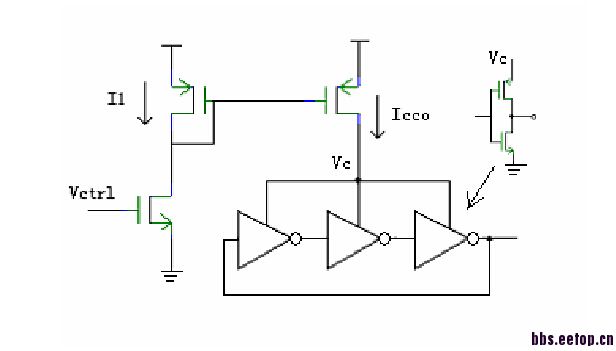

单端反相器延时单元VCO的相位噪声

我用90nm工艺,1.2V电压,仿真显示输出波形峰峰振幅只有0.5V左右,按理说这种结构振幅可以达到接近满摆幅,请问改变什么参数可以增加峰峰振幅,仿真相位噪声显示频偏1MHZ为-96dbc,这个结构有哪些方法可以更加优化相位噪声性能?

你把输入的I1变大,减小Icco到I1的比例,会使相位噪声变好,还有就是inverter的尺寸更大,但是会导致震荡频率上不去。-96dB到底好不好还要看你的震荡频率现在有多高。你这个结构太简单了,PSRR是个问题,一般都不直接电流偏置,用个类似LDO的形式比较好,有时候为了PSRR更好,输出的地方还多加一级gain boost。

振荡频率在200M到400M之间,-96db到底好不好还要看你的振荡频率现在有多高?请问这句话怎么理解?

把相位噪声折算成jitter是要除以频率的,例如,1G时候-96dB要比400M时候-96dB好大概8个dB。

以前做的0.18工艺的类似结构,400MHz频偏1MHz相噪大概-105dB,整体功耗大概是4mA。

可以增加vc上面pmos尺寸,会增加振幅。

delay cell可以做成两个inverter差分输出,两个差分信号用两组inverter反接提高翻转速度。最后差分转单端输出。

仿真显示输出波形峰峰振幅只有0.5V左右,这个不太正常 ?

有好点的结构么 我想做个450M左右的 。35工艺 稳定点的

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:hspice 波形仿真显示no data in design. select run hspice to create data files

下一篇:我在使用Verilog-a仿真,现在已经写好一个模块的Verilog-a,该如何写一个testbench