带隙整体仿真和单独仿真结果不一致

录入:edatop.com 阅读:

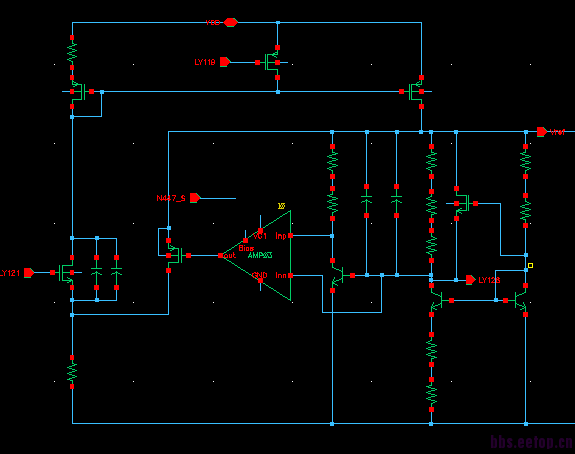

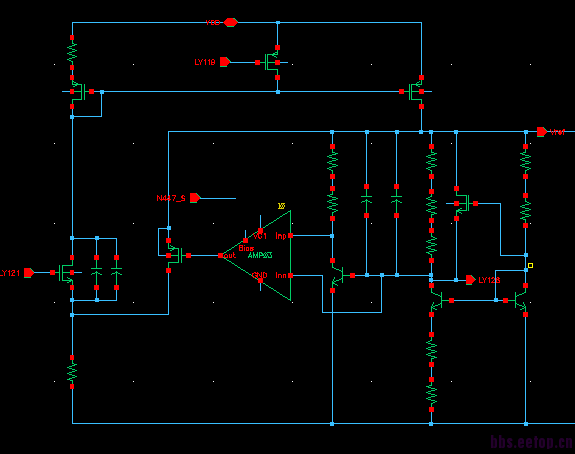

我反向设计的DC-DC模块中单独仿真带隙的是想要的1.2V带隙,但是放在整体电路中带隙的输出就是1.35,反正差别比较大,有大神遇到过这样的问题吗?一直找不到原因所在。电路结构如图。跟那个运放的反馈环路稳定性有关么?

不可能

你自己的问题,电源,地,还有输入输出,pin控制等出问题了

有可能是负载阻抗发生变化了

查查有没有漏电的支路

1.2V偏到1.35V已经不是环路不稳定造成的了,感觉应该是哪条支路灌下来一路电流~

应该是这样

对对对,有额外的电流灌下来了。我查到问题了

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。