vco噪声问题

增加偏置电流

看噪声总结,找到来源,从而找到解决方法,如增加LDO输出电压以增大摆幅和相位噪声,加大偏置电流,偏置上加RC滤波,优化LDO噪声性能等~

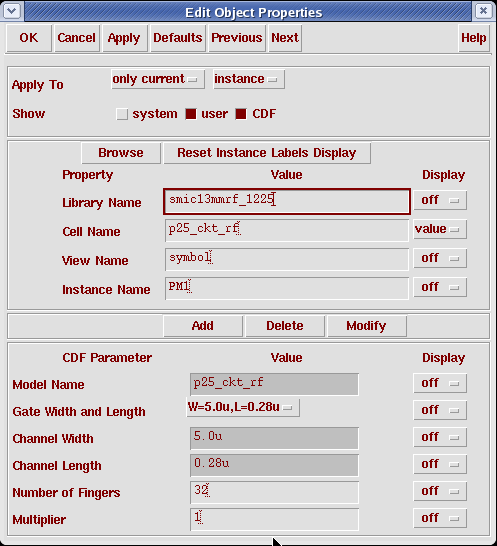

我看了是NMOS的闪烁噪声最大,应该是把L调大吧,但是我用的是SMIC 0.13的库,L很不好调啊,还有库里面MOS 的number of fingers参数是什么意思啊?我师兄说是对w的乘积,但是我仿了一下好像不是啊,不知道是我仿得问题还是什么问题,很郁闷,可调节参数如图

自己顶一下,请高手指点啊

估计你电压偏置的vco振幅太大了,导致flicker noise混频加重;

限制一下振幅,flicker noise会改善——可能会恶化一点thermal noise——找一个平衡点吧;

1M频偏-130dBc的噪声并不容易,需要优化包括LDO在内的每个模块——我做过的还没有这么高要求的,惭愧~~~

还有一点,SMIC的noise model很不靠谱~~~我跟他们的model的人因为noise model有过联系,两三年前的事了。

谢谢您的回答,还有我仿得差分电感的Q值在5G时为52,Q的半径为30u圈数为2圈都是最小值,是不是太大了啊,而且他的差分电感只有两端没有接地端,很奇怪啊

能仿出Q值50,估计哪里出错了吧~~~片上电感的Q值一般<15

要求有点高乐

@1MHz -130dBc/Hz? 频率多少,离开频率谈这个指标没意义。

中心频率是5GHz

按这个指标,如果功耗小于10mw都可以算是一流的VCO了。我觉得靠谱点,还是控制VCO的增益,降低。采用小电容,大电感,然后震荡到5G,加大电流。我觉得这个指标的提出,可能老师都没有认真衡量过。

为什么要用小电容大电感?这样用有什么好处?

smic的电感本来就一般 所以你只能用功耗来换

电压偏置VCO 低频相味噪声较差,主要是由于上变频增益较大,但是频偏大时相位噪声优势就体现。-130dBc/Hz@1MHz@5GHz的要求很高了,看你老师对哪方面的要求高了,若是又要高性能又要低功耗同时面积还有限制,那么这基本上很难做到。若是对面积的要求不高,可以尝试噪声滤波,这样可以提高3~5dBc/Hz,若是对功耗要求不高,可以采用较大的摆幅,但是这个也有限制,拜服大了有时噪声还会差,这个自己去调,最后若是都不能满足,试着改变VCO结构,不一定要采用电压偏执型。最后就是你电路调好后,版图设计还是一个大难题,没有大半年对VCO 版图的优化及理解是不可能第一次就画出高性能的VCO 的,加油吧

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。