Delta Sigma 问题

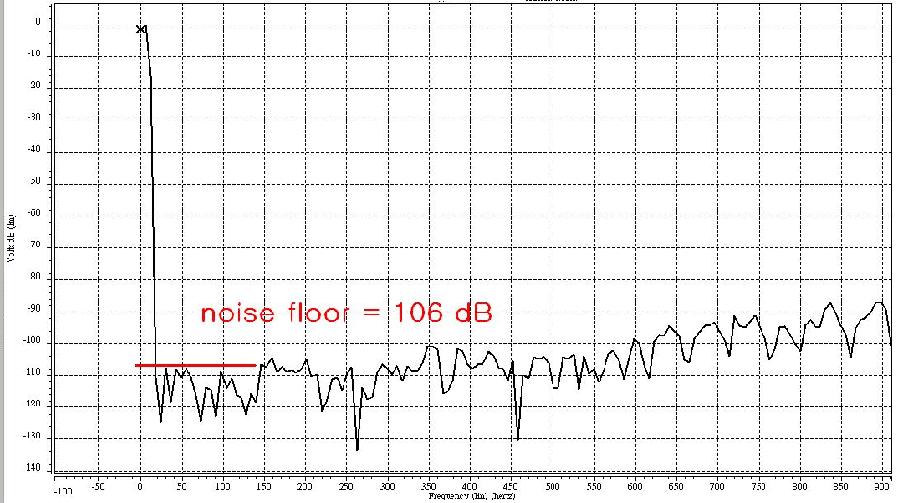

但是最后FFT结果却不如预期,noise floor 很高,

原本behavior model 可达到130dB,

请问有什么建议吗?

(OPA gain = 70dB, OSR=2048, BW=50Hz)

FFT

fft的问题,连信号都没分辨出来

Caosl你好:

请问为什么信号没分辨出来?

(我的输入信号是DC直流)

matlab sim 和 hspice 得fft points 是一样么?

matlab sim 有加上opamp bandwidth 和 opamp gain 么?

hspice sim 结果试试用hanning window.

vdslafe你好:matlab sim 和 hspice 得fftpoints 一样,

matlab sim 有加上opamp bandwidth和

opampgain,

请问hann的window会比较好吗?

请问charge injection 要如何解决?只要用non-overlap clock即可吗?

non-overlapp clockgen 不能解决charge injection

charge injection 可以用bottom plate sampling, 加dummy 和 differential 来处理

你得noise floor 其实是在-120dB 左右

还有可能是被hspice 得精度设置限制了

谢vdslafe:

再请问hann的window会比较好吗?

减小spectral leakage.

你要看这么低得noise floor。不用 window fft 是不行得

谢vdslafe:

再问一问题,您说被hspice 精度设置限制了,

因为我有下.option accurate命令,

所以精度是指点数fftpoints太少吗?

点数太少

建议输入交流信号,取hanning窗,做fft

请问输入交流信号后,做fft,

看到谐波(HD3)很大,

这是什么原因?

说明要不你给得信号太大了,modulator overload, 或者是你电路没设计好:)

感谢vdslafe:

我的系数跟matlab系数一样,输入信号magnitude = 0.7*Vref

应该不会错。

但是我的架构是feed-forward,

而second stage后的电容,大约是1/4倍的firststage电容,

是否会造成charge injection或clock feed-through现象?

看看你采样switch把。

把它换城理想得,看看怎么样

看来eetop真是藏龙卧虎阿,正在学习中,收获不小。

继续观望

学习中,高手好多

obviously, noise shaping isn't work!

learning now !

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。