Fold cascode OPA設計問題

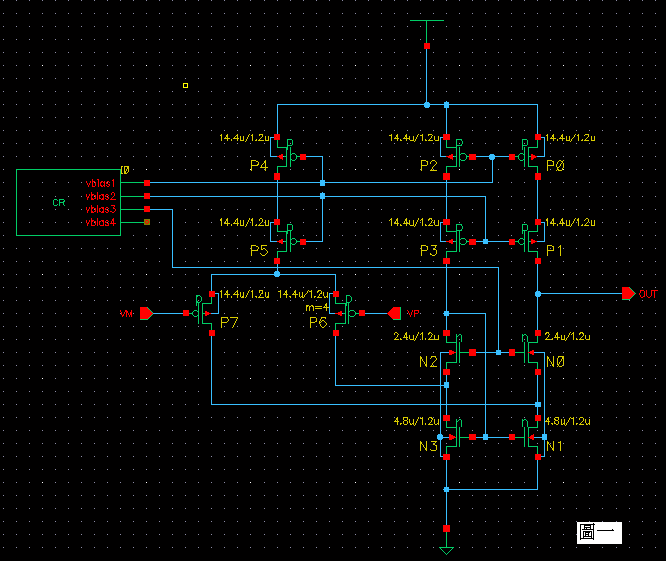

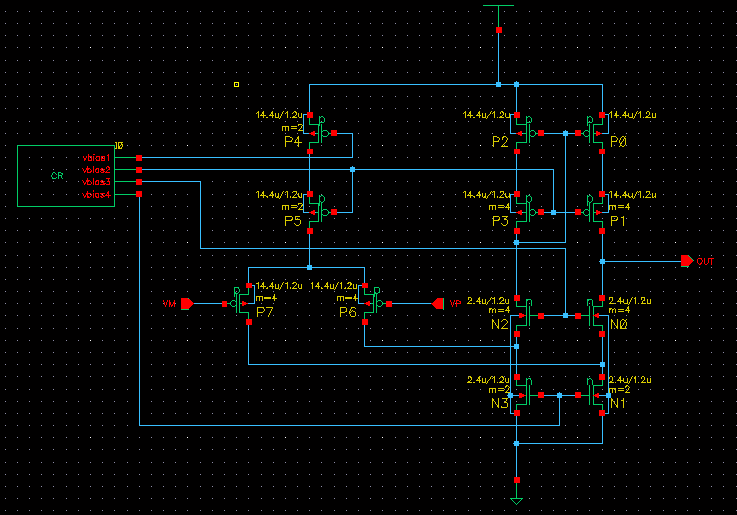

我想從數位領域轉往類比領域,所以我練習了這一個fold cascode OPA(圖一),我聽從建議

先設計bias電路(圖二),有了bias電路後,我想因為此bias電路也是cascode架構,所以OPA

電路的cascode架構中的mos w/l比應該要跟cascode架構的mos w/l比相同,如此偏壓才會使所

有的mos都在飽和區,請問我的想法是對的嗎?

還是bias電路負責產生電壓,OPA中cascode架構的mos w/l可以另外設定,只要bias電路

產生的電壓能使OPA中的cascode中mos都在飽和區就好?

此外從佈局(layout)觀點來說,bias和OPA的cascode中對應的MOS是否要一起做同中心(common-centroid)佈局?

(對應例子:OPA的P0,p2對應bias的p0,p3)

還bias的p0,p3做同中心佈局,而OPA的P0,p2另外做同中心佈局?

謝謝

圖二

圖一

小编你的fold cascode OPA有问题,上下电流源和电流镜的位置反了。三路的电流设计也有问题,建议可以先看看Allen书上关于fold cascode OPA的设计。你的偏置电路要加一个合适的启动电路。偏置电路和fold cascode OPA的偏置管的宽长比不需要一模一样,这取决于你需要的电流。但共源管与共栅管的宽长比之比与bias电路的一致最好。

bias和OPA的cascode中對應的MOS是否要一起做同中心(common-centroid)佈局,不需要。謝謝您的回答。

我比較了一下確實是與allen的書不一樣,再看了Razavi的書後覺得您是對的,我的電路是依Baker的cmos circuit design, lauout, and simulation P715畫的,我沒畫錯,所以是Baker的書錯了,可能是這個原因造成其他怪怪的問題。

>>三路的电流设计也有问题

因為大陸與台灣用語不同,請問您說的三路是指何處?是OPA電路的三個電流路徑嗎?

又有何錯誤?

>>你的偏置电路要加一个合适的启动电路

我會加的

謝謝。这种foldcascode结构没有问题,只不过大家都习惯看常规的,电流镜在上面的而已,并不代表这个不多,其实效果都是一样,无外乎是电流在何处求和而已。R-t-R结构的一边不就是这样的嘛。

知道,謝謝。

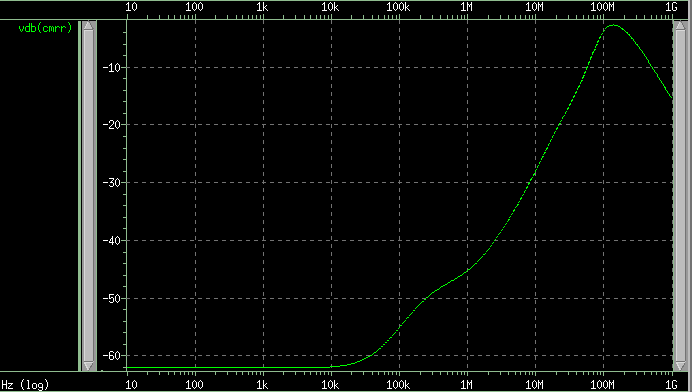

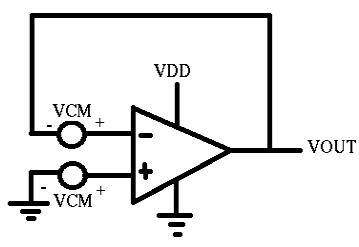

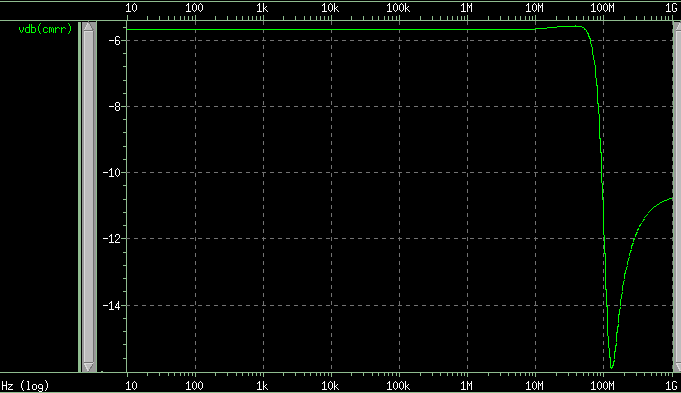

但不明白為何current mirror在PMOS處的CMRR是負的,如圖一,如果current mirror在NMOS處的CMRR是正的,如圖一上下相反的波形。

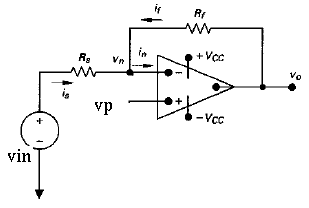

此外我將此OPA接成反向大器,圖二,其中:

rf : 10K

rs : 10k

vin : sin(1.65v 1.65 50k)

vp : 1.65

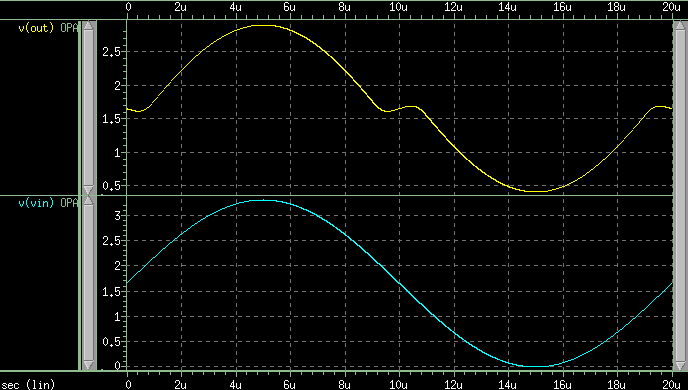

模擬結果如圖三,請問為何vin在1.65v附近時vout會出現怪波形?

PS : OPA的尾電流為20uA,而OPA cascode的電流都為10uA

新電路如圖四

謝謝圖一

圖二

圖三

圖四

OPA输出能够吸收和提供的电流能力只用30uA,你外部电阻设置为10K,而你vin加的峰峰值却是3.3V,

所以反相放大器没办法正常工作(看你的波形vout已经是跟随vin在变化了)。

恰恰是在vin在1.65V附近的波形才是正确的,你可以vin的峰值设置为10mv试看看。

你的图一表示的是-cmrr吧同一这位老兄的看法。30uA全流过10k的电阻也不过1.65+10k*30u=1.95V。

另外一个问题,象这种高阻抗的folded-cascode不适合这种驱动低阻抗的应用,因为amp的输出阻抗会小于10K(10K与ro并联).For Thincat

--> OPA输出能够吸收和提供的电流能力只用30uA,你外部电阻设置为10K,而你vin加的峰峰值却是3.3V,

--> 所以反相放大器没办法正常工作(看你的波形vout已经是跟随vin在变化了)。

--> 恰恰是在vin在1.65V附近的波形才是正确的

原來如此,受教了。我有將峰值设置为10mv,OPA的輸出是有反向效果,不過gain小於1,理論要是1才對。可能如Ryu所說的是阻抗匹配的問題吧。

-->你的图一表示的是-cmrr吧

我是要量CMRR,但不知CMRR有負的,我用下的code來求CMRR的,如果currenct mirror在cascode的NMOS端,則CMRR為正的,反之就成負的,不解。

.param vdd_p=3.3

vdd avdd 0 vdd_p

vss avss 0 0

VM VM VP dc 0v

VP VP avss dc 1.65v ac 1v

* instance of top module *

x1 OUT VM VP OPA

* Sweep & Analysis *

.op

.ac dec 100 10 1000meg

.probe ac cmrr=vdb(OUT)

謝謝指教

For Ryu,

謝謝您的解釋,請問像這種高輸出阻抗是如何量output swing?

我的方式為:

* Power *

.param vdd_p=3.3 vcom_p='vdd_p/2'

vdd avdd 0 vdd_p

vss avss 0 0

VP VP avss dc vcom_p

* instance of top module *

x1 OUT VM VP OPA

R0 OUT VM 10k

R1 VM vin 10k

vin vin 0 sin(vcom_p 1.65v 50k)

* Sweep & Analysis *

.op

*.DC vin 0v 3.3v 0.1v

.tran 1n 20u

* Analysis Output *

.probe dc v(*) i(*)

謝謝。

共模抑制比CMRR为差模电压增益与共模电压增益之比,并用对数表示。看你的代码好像求的是共模电压增益(而且没有设置好合适的直流偏置点,即直流为开环接法),记得allen的书中有讲cmrr的仿真方法,你可以去看看。

不知道你要用在什么地方,如果是switced circuits的话,可以把VM与OUT直接接上,sweep vcom_p, 看VM和VP的差就可以了,不过你要弄清楚你到底需要做到什么样的指标。最简单的,open loop也可以做的,例如你要60dB上的gain,你sweep VM和VP的差分输入,看gain>60dB以上的输出范围就是你的output swing。

如果你是要驱动低阻抗负载的话,例如你的应用和你的测试电路相似,那么,我想你首先还是考虑加输出级把输出阻抗降低为好。我看了,allen提供兩個方法(figure 6.6-6和figure 6.6-7),其中figure 6.6-6太麻煩,所以我選用figure 6.6-7的方法,我修改的spice deck如下:

.param vdd_p=3.3

vdd avdd 0 vdd_p

vss avss 0 0

*VM VM VP dc 0v

VM VM OUT dc 1.65v

VP VP avss dc 1.65v ac 1v

*************************************************************************

* instance of top module *

*************************************************************************

x1 OUT VM VP OPA

*************************************************************************

* Sweep & Analysis *

*************************************************************************

.op

.ac dec 100 10 1000meg

.probe ac cmrr=vdb(OUT)

跑出來的結果為圖二,很奇怪,不對,能否請您跟我說如何才是對的方法。

謝謝figure 6.6.-7

圖二

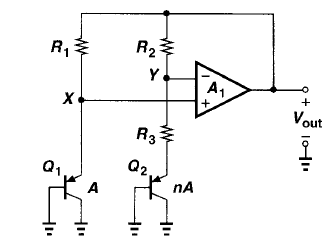

如第一篇說的,我只是想要學analog IC design,不過我想將此OPA用到bandgap上,如圖,這樣的應用應該不會有阻抗匹配的問題吧。

另外您說"最简单的,open loop也可以做的,例如你要60dB上的gain,你sweep VM和VP的差分输入,看gain>60dB以上的输出范围就是你的output swing",因為我剛入門,所以不是很懂您的建議要如何實做出來,您能否更進一步說明?

謝謝

fold cascode OPA有问题

不懂您說的地方在哪裡,能說清楚嗎?

I learn a lot from the above disscusions, and Thanks for your sharing.

Beside those, There may be some Matching and Area problems for PMOS, I think, for Layout.

Matching & Area Issues:

Although PMOS's Source terminal can be connected directly to the Nwell, the such connected Cascode PMOS pair (e.g., P1 & P4 in the Bias circuit and P1 & P3 in the Cascode OpAmp) can not be included in the same Nwell, which degrades the matching accuracy. Meanwhile such connected the PMOSs need individual Nwell, takes more area, 'real estate' !.Thanks. For a new guy in analog desing, your message is very very useful. You're welcome for giving me more your experience.

Thanks again.小编偏置管子尺寸有问题

偏置好几个管子尺寸都有问题啊 怎么都一样

bias的P2和n4 length不同,P2是用來產生P1,4,7的偏壓而N4用來產生N0,2,5,的偏壓,請問您說的"偏置好几个管子尺寸都有问题啊",是何處?謝謝。

应该是:

VM VM OUT dc 0 ac 1v

VP VP avss dc 1.65v ac 1v

VM与out之间直流电源为0,交流源为1

VP与地之间直流源为1.65,交流源为1当不了沙泼还是要支持的!感谢感谢~

goode man

上下电流源和电流镜的位置有什么讲究的地方吗?两种接法好像都没问题

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:仿SR的时候底部有过冲

下一篇:1.2V的管子用在1.5V 或者1.8V