请问各位setting time跟什么有关呢?

我仿真的时候接成单位增益缓冲器,另外加了5pF负载电容

带宽啊,首先,降低你的增益,去提高带宽,在保证gm不变的情况下,把你的输出电阻降低,此时你的主极点会远离原点,即你的-3dB带宽会变大,增益带宽积就会提高。setting time 和你的增益带宽积有关系,即和你的-3dB带宽有关系。

测试建立时间,运放接成单位增益负反馈形式即可,无需加负载电容.(加负载电容,那是测试SR,压摆率)。

测试建立时间时,你添加的阶跃信号幅值大小和你的阶跃信号延迟时间T,构成的阶跃信号,通过运放进行发达,时域信号,转化成频域时,频域的高阶成份,的频率不能超过你的-3dB带宽,否则,运放响应很慢。你的上升时间会很长。

把带宽提高了,相信你的setting time 就能符合要求了。

其次,我也是模拟IC刚入行,目前也正在折腾折叠式运放。

不知道小编可以把要求的指标共享一下吧。

一起交流一下。

呵呵,我也刚入门,导师的要求下看了半学期书和做习题,主要看Razavi的,现在边做电路边看ALLen的,感觉对设计很有用,还有池宝勇的

理论上18M GBW的到90%的settling time 就是20ns

10M GBW的settling time 也有40ns,你的才2us,slew rate太低了?

是的,我不清楚SR和setting time之间的关系,请问下您它们之间有相关公式吗?

增大电流后,看看是不是变高了

你是说增大压摆率吗?我尝试一下,其实我已经用的很高的电流了(差分输入管和折叠共源共栅支路各40u),总共要求不超过150u

负载加电容了吗?应该有一个10p的电容

加了5pF的负载电容,而且这个负载电容是系统要求,不能改;要求折叠式共源共栅部分和偏置部分总共150uA左右。

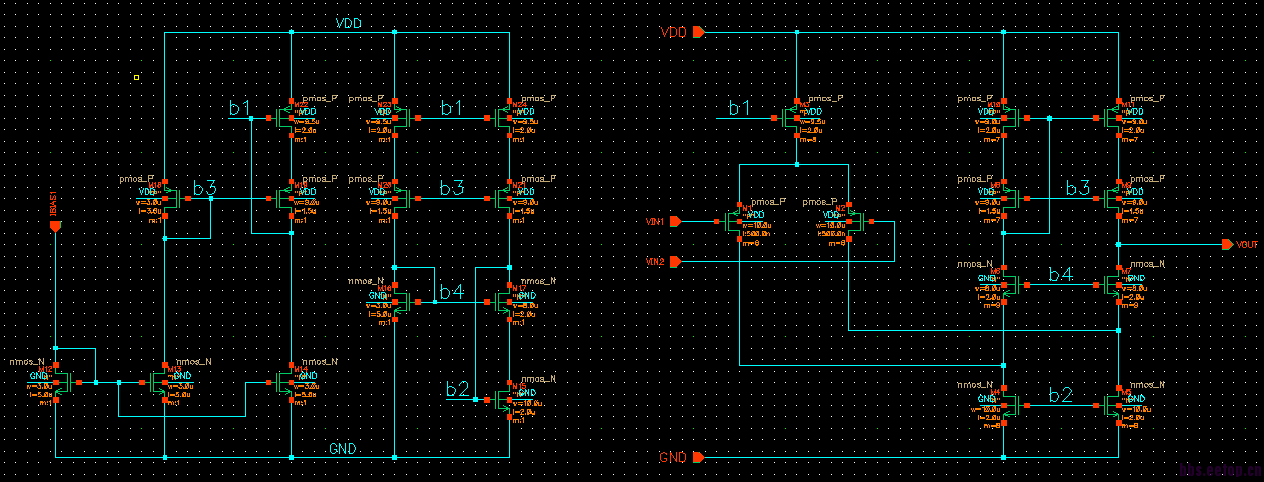

偏置电路的电流是不是可以很小,我的偏置如图所示,5条支路,每条支路电流大小一致;如果我给IBIAS一个3uA,那么偏置电流共15uA是不是有点多啊

迭代一下栅长

我附上的这个图是仿开环增益,相位,setting time等,达标后就要接成双端输出了,还要加共模反馈。

折叠cascode的输入支路电流和套筒支路电流对于SR的关系,请参考拉扎维和马丁的教材

谢谢您

什么工艺?

5V,3V还是1.8V?

哦哦,5V的工艺,

如果只是电压偏置,电流可以很低,只需要电压达到要求就可以了,电流增大我指的是运放的电流增大.

真的奏效了,我的gm提高的情况下,把输出阻抗降低,这样增益提高的同时带宽也提高了,测setting time的时候现在只有100多ns了,离20ns的要求更近了,继续是输出阻抗变小,相信会满足要求的!谢谢~

您是说只增大差分管的尾电流,还是差分管和共源共栅支路都要增大电流?

尾电路

输出电阻降低之后,增益就会降低,主极点增加,但是GBW不会变的呀。

setting time到底怎么样才能降低呢?我之前把输出阻抗降低了,建立时间确实降低了不少,但是没达到想要的效果,管子的长已经不能减小了,到500n~1um地步了

除了增大电流,还有有其他办法吗,在增大我就电流超标了

如果对增益要求不高的话,可以把P_coscade 砍掉一级试试

客气了,settingtime和增益带宽积(即-3DB带宽的频率有很大关系),如果输入的阶跃信号产生的高频成份大于-3DB带宽的频率,那么建立时间肯定是加长了。(至于这个阶跃信号产生的高频成份,也就是这个最高的频率。目前我也在计算。摸索中。在看信号与系统这本书。)尝试满足增益要求的前提下,提高你的-3DB带宽,相信,会减小你的settingtime的。有问题一起交流。

提高-3db带宽的频率的话,共源共栅管子的尺寸得非常小了!我目前调出的指标是达标了,但是功耗增加了不少(输入管尾电流增加了很多,共源共栅支路同样的增加)

嗯嗯,谢谢建议,我试试

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:拉扎维 中文版 图10.21 极点合并

下一篇:VCO ,LNA 和MIXER在一个片内情况下,作LNA和MIXER的cadence仿真电路