ADC中SH电路的建立过冲问题

录入:edatop.com 阅读:

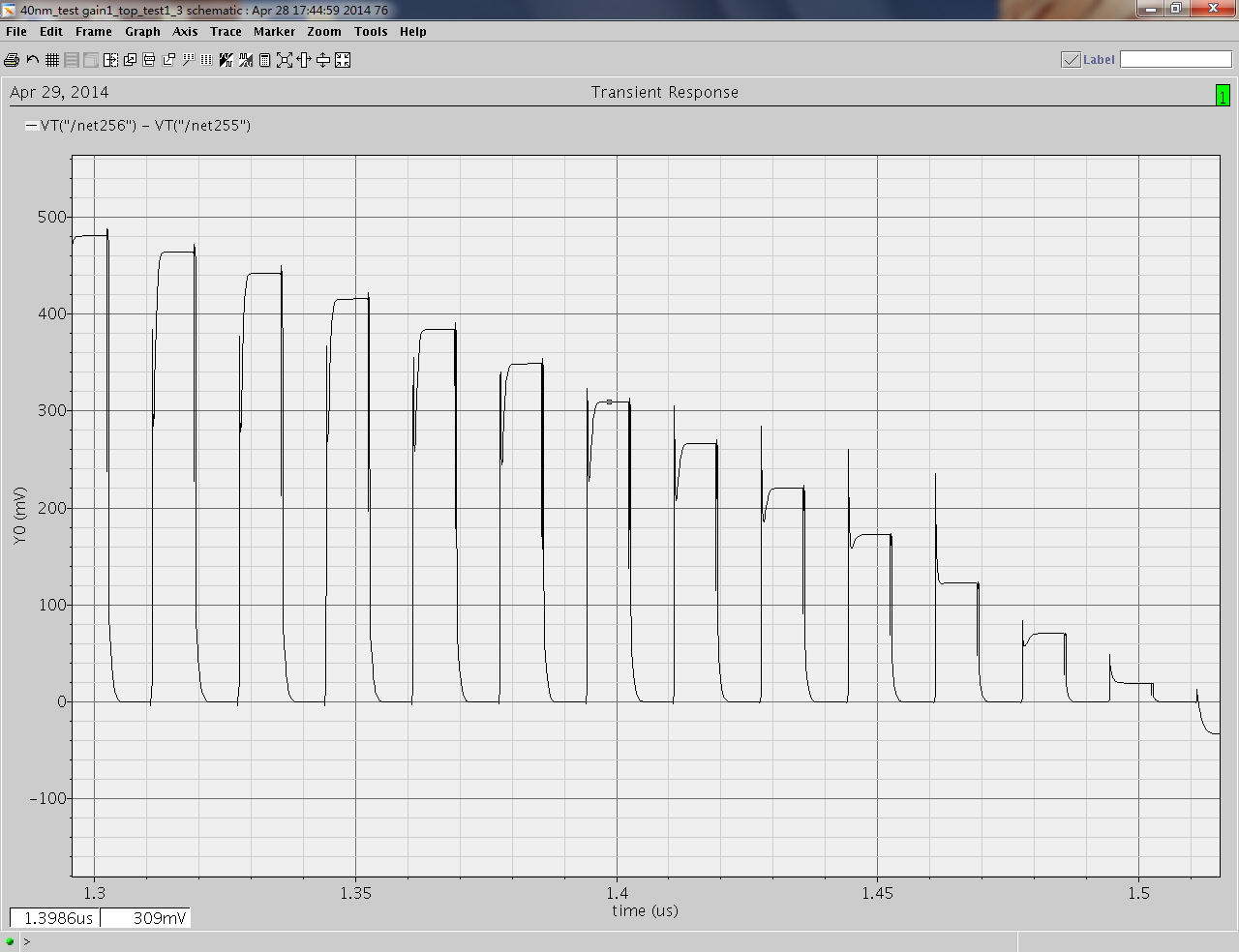

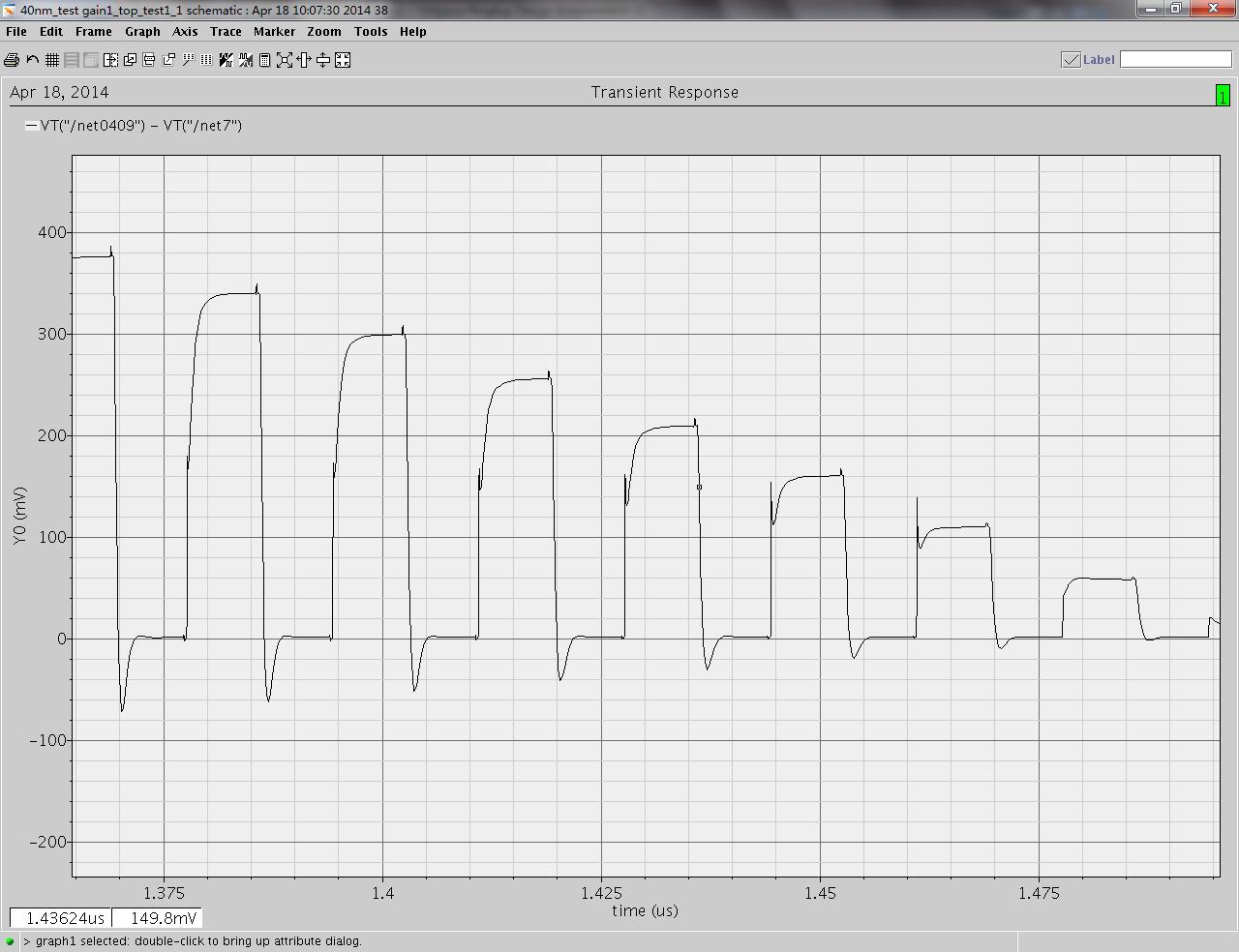

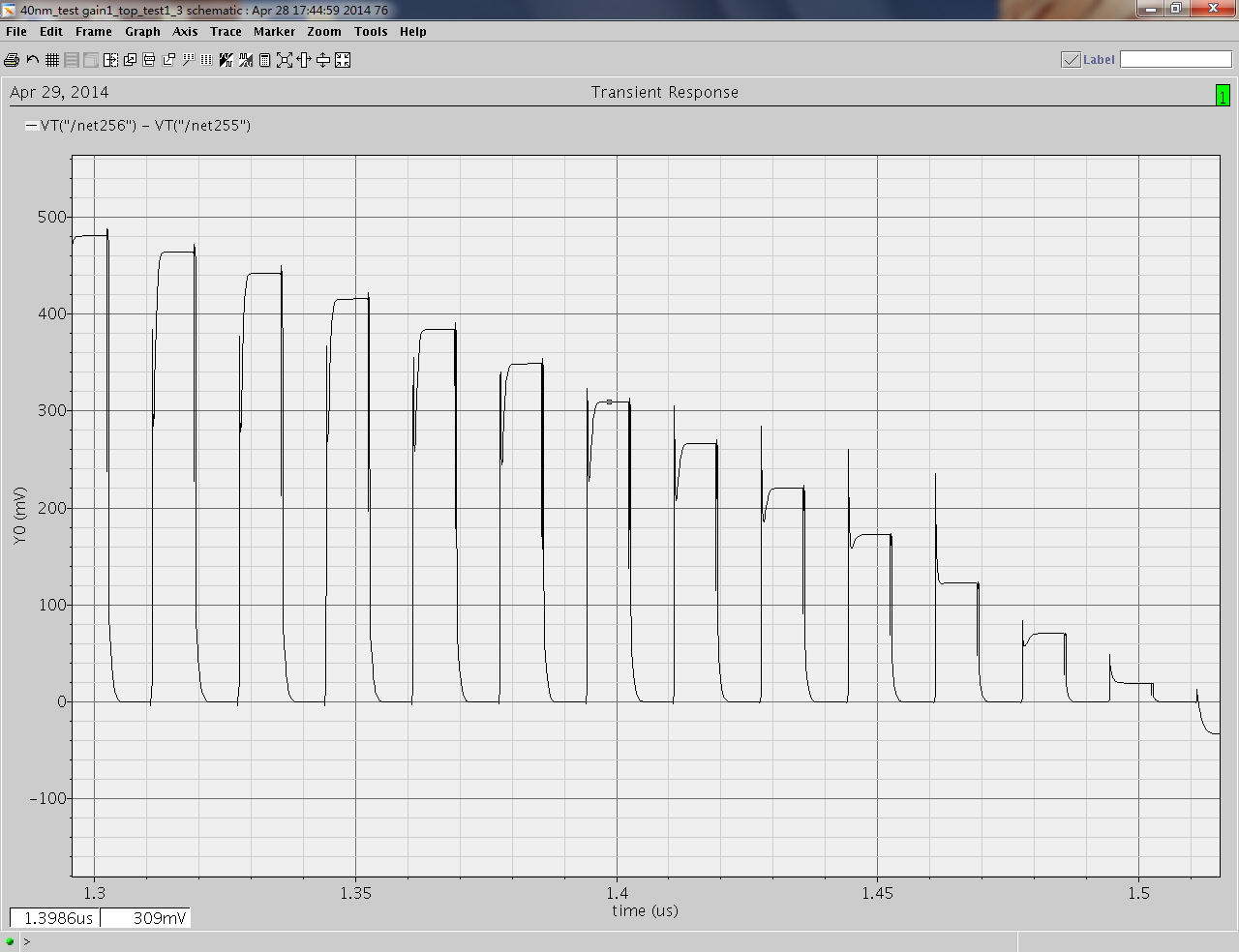

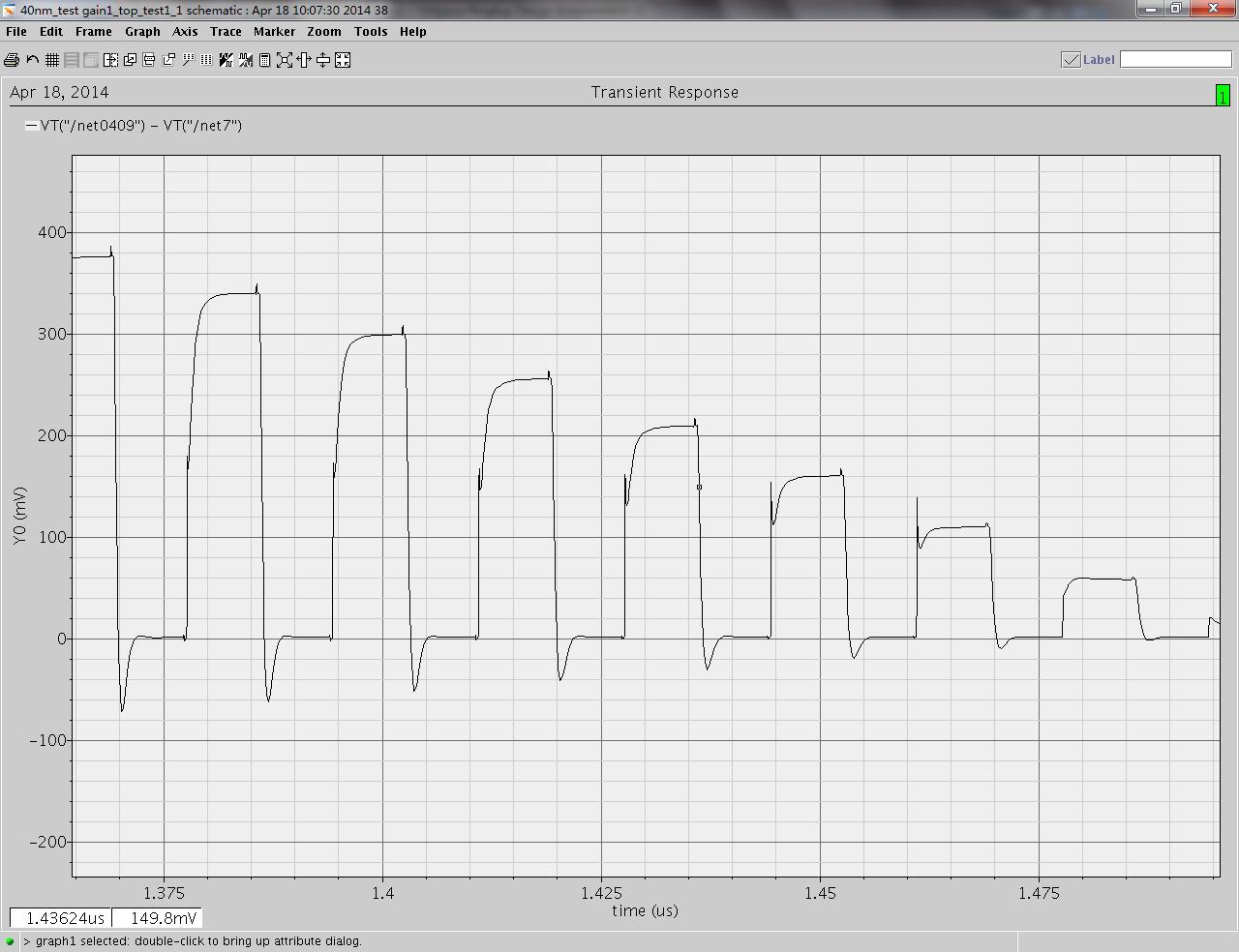

在运放完全满足条件的情况下,小信号的建立过程中出现了过冲的问题,运放的相位裕度和带宽是满足要求的。不知道开关是不是要和运放匹配,设计开关的时候是否应该考虑运放的主次极点的位置。图一是理想开关(带20欧姆的电阻,没放电容)情况下,采样的状态,幅值较小的时候的过冲是时钟引起的,但是能够很快平稳下来。图二是普通PN对称开关的情况下,采样的输出,在回到零点的时候有一个很明显的过冲,这是为什么。图三是普通PN对称开关的情况下,第一级的输出,可以看出,在幅值较大的时候,有过冲+震荡,在小幅值的时候完全震荡,不能建立。运放的相位裕度>60,对比图一是不是说明是开关尺寸的问题,现在开关用的尺寸非常大5--10u/45n,应该怎么解决,需要用栅压自举开关吗,做的是60M的ADC。初学者,请各位看官给与帮助,不胜感激。

有人吗

自己顶

怎么没有回复啊,我也很想知道,关键是在低电压时噪声更大,啥情况,能把电路图贴下不

LZ交代清楚啊,45nm多少的电源电压啊,这开关的尺寸太大了!

1.1V电源电压

小编发的第一张和第二张图所列出的现象,我也遇见过。不知道小编是否仿真过放大器的共模反馈的AC特性。

第三张和第四张的情形没遇见过。

仿过,运放的带宽很足,相位裕度也在60度以上增益也够

錯開吧 !

不错。

阈值电压多少?

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇: 90nm 65nm 45nm 下各金属层和ILD厚度

下一篇:关于RF电路后仿的问题