怎么制作尺寸可调的逻辑器件的symbol《已解决》

问题:我想制作尺寸可调的逻辑器件的symbol

以下第二个图为例,直接修改pmos,nmos宽长比即可(图中白色字体即是

我的解决方法及所遇问题:

方法:使用pPar

1,在内部schematic里管子的参数里面填pPar("wp"),pPar("lp"),pPar("model")...

2,然后在inv这个下面的cdf里面加上w,l,model...

问题:

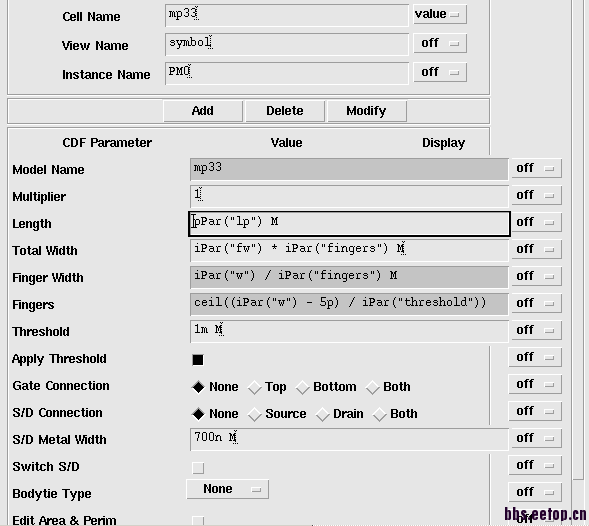

1,如下图所示

修改完length,一切良好。

修改total width时,本想修改为pPar("wp"),但是当修改完成时,就变成了如上图所示。

然后我保存设置,就直接跳出了cadence

参数都用pPar, 不用iPar。

不选“Apply Threshold‘,让Finger Width和Fingers都可以填。

Multiplier:pPar("mp")

Length: pPar("lp")

Finger Width: pPar("wp")

Fingers: pPar("fp")

保存后直接creat symble,就会把参数传递。

大神,谢谢哈!纠结了好久,祝您生活幸福ok 还不错

我也是这样调用的,symbol顶层没有问题,但进入到这个cell的schematic,发现里面会显示error,

比如W。请问这是什么原因呢?望赐教。申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:一种Poly fuse trim cell里PMOS上拉管的作用

下一篇:关于spectreRF simulation 仿真问题