模拟电路中ESD问题请教各位大侠!

只是我们想分析他们的结果)

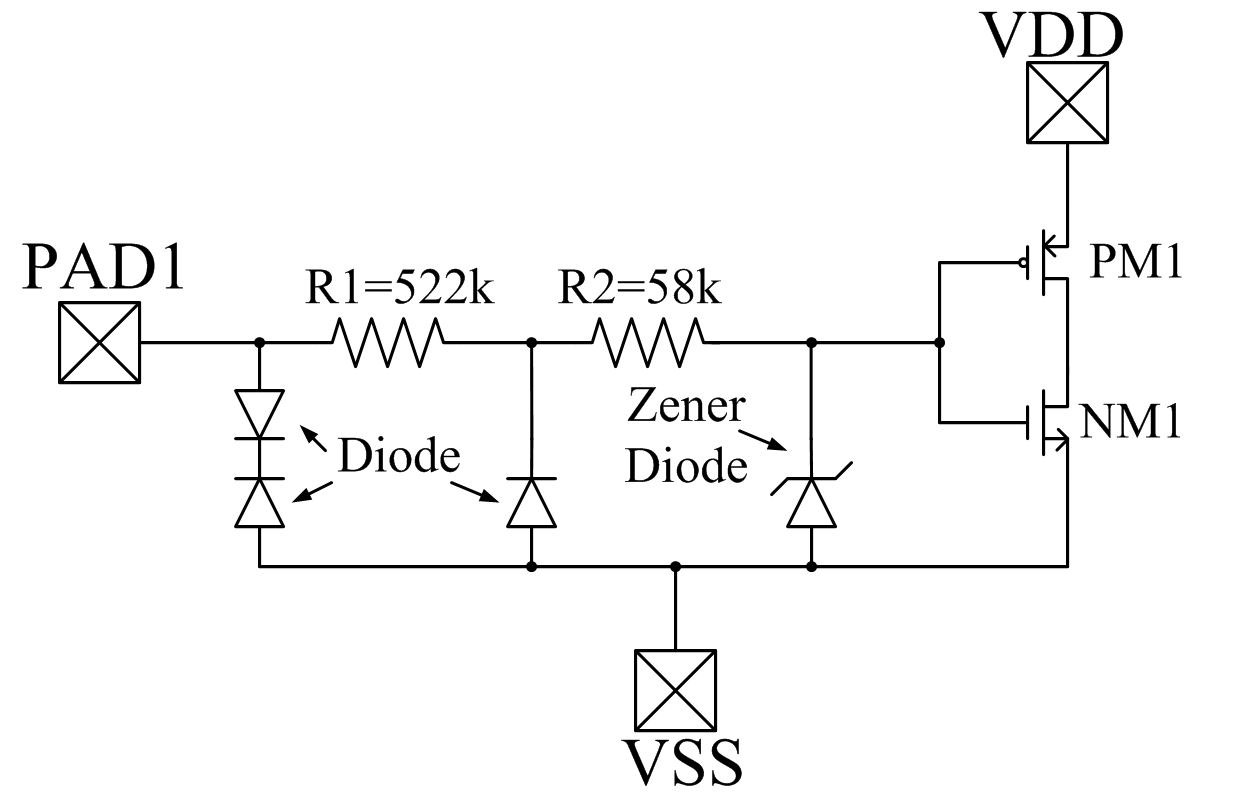

就是附件中所述的引脚PAD1对引脚VSS打正2000V(即PAD1为电压正端,VSS为电压负端)时,PAD1对VSS

的IV曲线在打ESD前后没有变化(说明PAD1对VSS的ESD防护没有被打坏),但是导致芯片引脚VDD对VSS之间有漏电,

不知道有没有人碰到过这个问题?什么机理呢,请教过程中。

看看电路中是否存在悬浮节点,可能是esd过程在某些节点上充电了,但有不能完全放掉,是vdd到vss的某些东西在低阻态,你就看到漏电了。

或者是耦合过去了些信号,损坏了什么。

外人只能猜,还得看电路,layout和实际测试现象才能解决

觉得有可能这个ESD zener那里电压抑制不够好,PM1的gate和衬底nwell穿通了。

在测漏电的时候,如果PAD1悬空,会测到有个电压值吗?

看这个ESD电路结构,PAD1的正常工作电压似乎较高,是多少伏啊?

还有普通标准CMOS工艺是实现不了正向PN结的,图中的这个正向PN结是通过DNW来实现的吗?

他这个正向PN结和后面的一个反向串联,可以用“P注入+N井+P衬底”实现。

请问测到漏电时,PAD1为何电位?如果反相器输入端电位接近1/2VDD,即使PM和NM没有打坏也会漏电。

是不是这个ESD电路有点问题啊,正向打ESD时保护能力不够,靠diode和齐纳管反向击穿来保护gate

那gate至少也要见到5~6V电压,会不会是打过ESD后阈值变化了,导致漏电。

再加一个ESD diode到电源,然后电源、地之间加一个clamp就好了

负向ESD打过么?那样应该没有问题

谢谢各位的回复,对的!我可能没有把情况说清楚,再补充一下:

此工艺不是普通的CMOS工艺,

BJT,CMOS等都有,二极管phvnw, hvpwhvnwnbl都有。

PAD1的正常工作电压范围:(-9V~22V),

MOS管的栅氧承受电压<7V,

VDD=2~5V,

我们也尝试在VDD与VSS之间加5V测漏电时,在PAD1上加一外加电压,电压值从0~5V变化,

试图改变芯片内部的高阻节点(悬浮节点)的点位,结果发现漏电流没有变化!说明此漏电流与

PAD1的电位没有关系。

还有我们在宜硕打ESD时,

用3个样品芯片PAD1对VSS打2000V正压时,有2个样品会VDD与VSS之间漏电,还有1片是好的(不漏电);

用3个样品芯片PAD1对VSS打1500V正压时,有1个样品会VDD与VSS之间漏电,还有2片是好的(不漏电);

用3个样品芯片PAD1对VSS打1000V正压时,3片都是好的(不漏电);

后来又重复进行了此实验打2000V,共有5片芯片漏电,

而且5个样品芯片漏电在VDD=3V时,漏电流分别为:194uA,193uA,194uA,195uA,196uA(即样片之间误差很小,只有1到2uA的区别)

改变VDD=5V时,此5个样品芯片漏电流都一样为:537uA(样片之间没有区别)。

即漏电与VDD之间不是正比例的关系,倒是有点平方关系(即:抛物线曲线),因为5/3不等于537/194.

而且漏电流的值可以重复,说明不是普通的击穿导致的漏电流(如果是普通的击穿导致VDD与VSS漏电流,则

漏电流值不可重复!)

对了,上面的附图是我能从芯片schematic中找到的PAD1与VDD最直接的连接关系了,不知道有没有其他的

耦合方式导致漏电了?

谢谢你的回复

你说的很有道理,我接下来可能就是找电路中间接的耦合点了

你说的没错,PAD1正常工作时为-9V~22V,高于VDD(2~5V),所以需要此类ESD。

你说的有道理,我们也曾尝试改变PAD1的电位,看VDD与VSS之间的漏电流,

结果发现漏电流与PAD1的电位没有关系。

谢谢回复!

电源VDD和VSS之间有CLAMP电路的(没有画出来),我们在对PAD1对VSS打正压2000V后,

会检查芯片所有的PIN脚的IV曲线,结果发现就只有VDD与VSS之间因漏电而使IV曲线不重合。

还有,我们单独对VDD相对VSS打正压2000V,也没有发现漏电问题。

BTW,PAD1对其正电源(另一个电源域VDH=10V,非VDD,VDH是里面升压电路产生的一个电压)打过

正压2000V和负压2000V,然后检查芯片所有的PIN脚的IV曲线,结果发现IV曲线都是OK的。PAD1对其正电源

的ESD保护也是OK的。

PAD1上面本来就串联了500k电阻,所以无论PM1是否击穿,PAD1电压的改变都对VDD漏电流影响不大。

如果PAD1除图上电路外没其它对地的电流通道,那测漏电时候PAD1的悬空电位可能会知道PM1是否击穿

看器件的名称这个是TSMC的0.25u BCD工艺吧? 图中接地的反向DIODE都是直接用的高压DIODE?是厂商提供的ESD器件吗?

谢谢回复,我们回头在侧漏电流时测一下PAD1的电位

不是T的工艺(出于对公司保密的考虑,不方便透露Foundry厂,望谅解! )

是的,因为分压原理,改变PAD1的电压不会显著改变PM1,NM1栅极上的电压

ESD电路里在电源与地之间有个东西叫 clamp trigger,你看下有没有这个电路。很多时候的这种情况都是这个电路没做好,一点被耦合触发就会有电源到地之间的漏电通路。

测pad1电压时,电表内阻一定要调高啊,感觉测出来的未必真实。

他这个不是你说的那种active clamp的ESD结构。与那个无关。

看来小编对ESD很有研究,有个问题想问下: 用3.3V I/O 器件做的5V tolerance ESD,能做到HBM 多少伏? 希望面积跟常规过8KV的面积一样大。能指导下吗?

或者说将PAD1接到地,然后串接一个万用表,看看有没电流流入地

zener内部串联电阻大,一些ESD资料说直接用作ESD钳位的话效果不好。见过类似的两级高压ESD结构,NM1的栅极就用小面积的常压GGNMOS作为第二级的ESD钳位

没搞过,不清楚。

谢谢大家的参与

刚又看了那5颗漏电的芯片的仅在VDD与VSS之间加电压(3V~5V)时的PAD1电压,

没有发现规律,电压在0~0.7V之间不定。PM1和NM1栅极应该没有被击穿。

可能是芯片里面的其它部分在打ESD时漏电了,继续排查……

而且这5颗漏电芯片在测漏电(即仅在VDD和VSS之间加2~5V可调电压)时,

当VDD从3V降到2V左右时,

漏电流从160uA突变到500uA,

然后再将VDD调回3V时,漏电流变为800uA(不是先前的194uA了),

电压VDD调到5V时,漏电流为1300uA,但是不能稳定住这个电流(过一会就又回到537uA了)

而且5颗漏电芯片都出现了大致相类似的症状!怪异啊

现象

如果PAD1接的所有电路如图所示的话,那理论上PAD1的悬空电压就是0V啊(diode & zener存在漏电流),这个0-0.7V是定电压吗?

有测过VDD供电,将PAD1接地串接一个电流表,看是否有uA电流流过电流表,然后流入地吗?

seeing

恩,谢谢

额,我的意思也是想看PM1到PAD有没有漏电。

谢谢回复

0~0.7V是一个飘忽不定的电压。

“VDD供电,将PAD1接地串接一个电流表,看是否有uA电流流过电流表”这个我也测过,没有电流流过

谢谢回复, PM1和PAD1之间确认没有漏电

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:这个SC积分器的传递函数?

下一篇:关于gm(基于cadence工具的学习)