请教只用条dummy poly而不是dummy transistor对匹配有没有好处?

录入:edatop.com 阅读:

我用的是.13的工艺

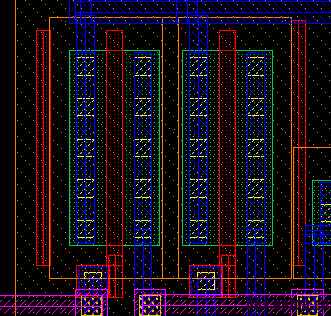

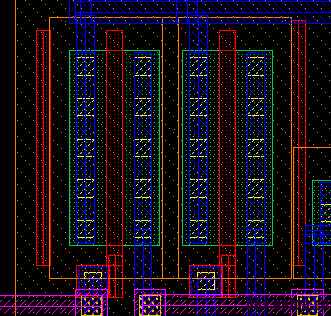

我看网上说要用个dummy管子来做匹配, 那就要G D S三端都要做。 但是我这里对匹配要求也不用很高, 我想只用个dummy poly来减小etching的影响就行了。 dummy poly 像这样行吗, 两边的两条poly还是floating的? 求指导

我看网上说要用个dummy管子来做匹配, 那就要G D S三端都要做。 但是我这里对匹配要求也不用很高, 我想只用个dummy poly来减小etching的影响就行了。 dummy poly 像这样行吗, 两边的两条poly还是floating的? 求指导

很多都这样

我用这个做lvs,会出warning说“missing connections STAMPing laye poly_nodev by layer poly_cont in cel xxx”. 如果我用poly_dummy这个layer来画dummy,就没有这个warning了。 poly_dg和poly_dummy这两层工艺上有区别吗? 是不是就应该用poly_dummy来画?

没区别,只是lvs或者drc的标示层而已,不加标示独立poly会被认为有个器件存在

怎么dummy poly的drc rule 跟普通poly的不一样啊, 差别太大了。

比如说, poly的最小宽度0.13um, dummy poly的宽度要0.6um。

PDK上说:The rule is for drawn dummy poly guideline purpose only. This rule is ignorable at designer's own risk.

一般能不能忽略这些rule, 就把它当普通poly来看待?

自己顶, 。

大侠帮帮忙吧

可以的。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:同一工艺,为什么基本上都是P管比N管得最小L要小?

下一篇:相位噪声ISF求问