带隙基准电压设计

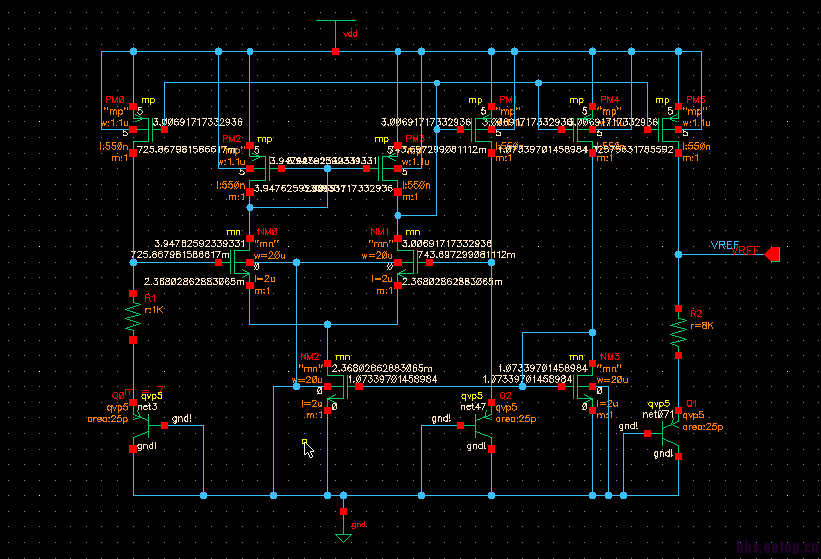

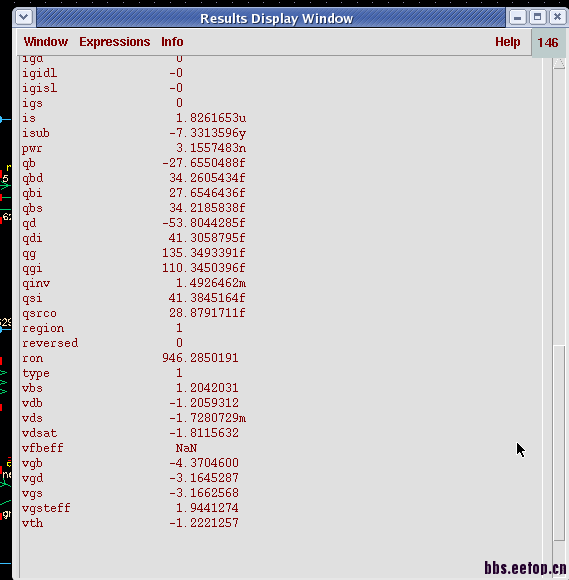

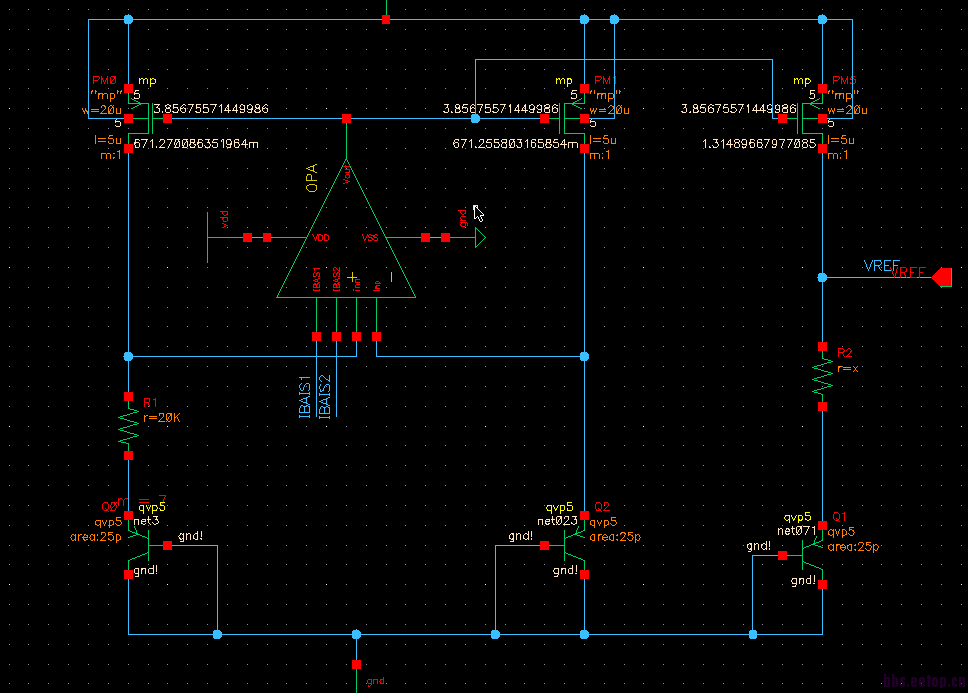

最近在仿真一个带隙基准电压源,这个是总的电路。仿真的时候发现NM0、NM1处在亚阀区,从而导致这两个管子的源级电压只有几个毫伏,NM2也截止了。我怎么调才能使NM0、NM1进入饱和区了。请大神们指教一下,小弟感激不尽!

最近在仿真一个带隙基准电压源,这个是总的电路。仿真的时候发现NM0、NM1处在亚阀区,从而导致这两个管子的源级电压只有几个毫伏,NM2也截止了。我怎么调才能使NM0、NM1进入饱和区了。请大神们指教一下,小弟感激不尽!

运放输入管换成P管哦

这个输入管尺寸做大,200u/1u,在看看

运放输入在0.6V左右,就算你输入对管的源为零,也不好开启呀,如楼上所述,换成p管输入可以避免这个问题。

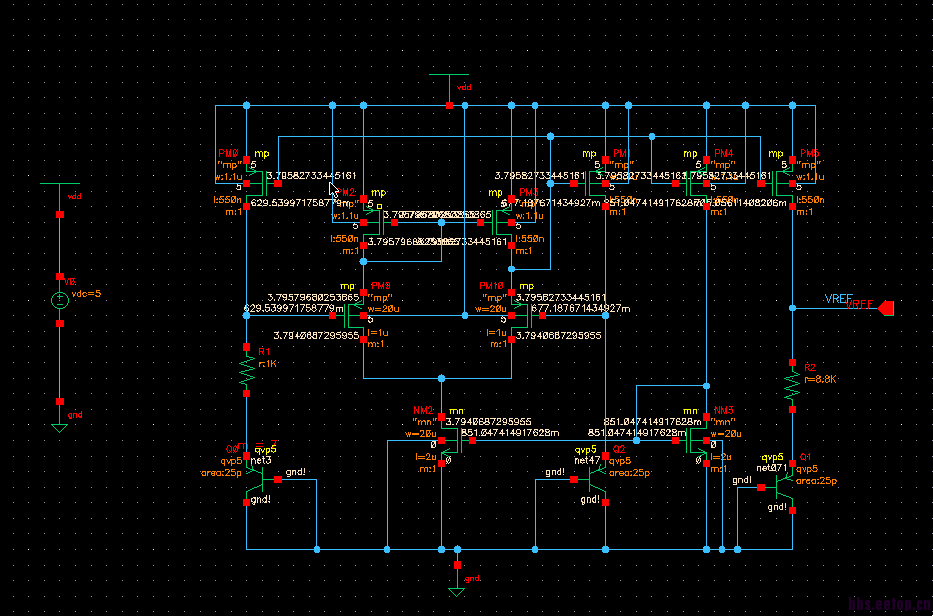

换过了这两个管子还是不行,出去截止区。这是为什么了?

换过了这两个管子还是不行,出去截止区。这是为什么了?

你调调偏置呀,你看看你的偏置电路,P管能打开吗?

还有P管输入,P管做负载,为什么不折叠?

我在试试。谢谢啊!

你PMOS输入对的运放怎么能这么搭?

输入管是换成P管了,问题是都不是“输入对”了。

输入为P管的运放不是这么搭的,你翻下书看下

这个电路能用

能用是能用,但是输出端在P mos的S端,这里得到的输出阻抗R小了点,整个OP的增益不大呀,做的没有意义了

建议换成P管输入

看得我想哭

巨型菜鸟,你多看看书啊。

PMOS管做输入对管,NMOS电流镜做负载,好好看下书,不要在犯这种错误了

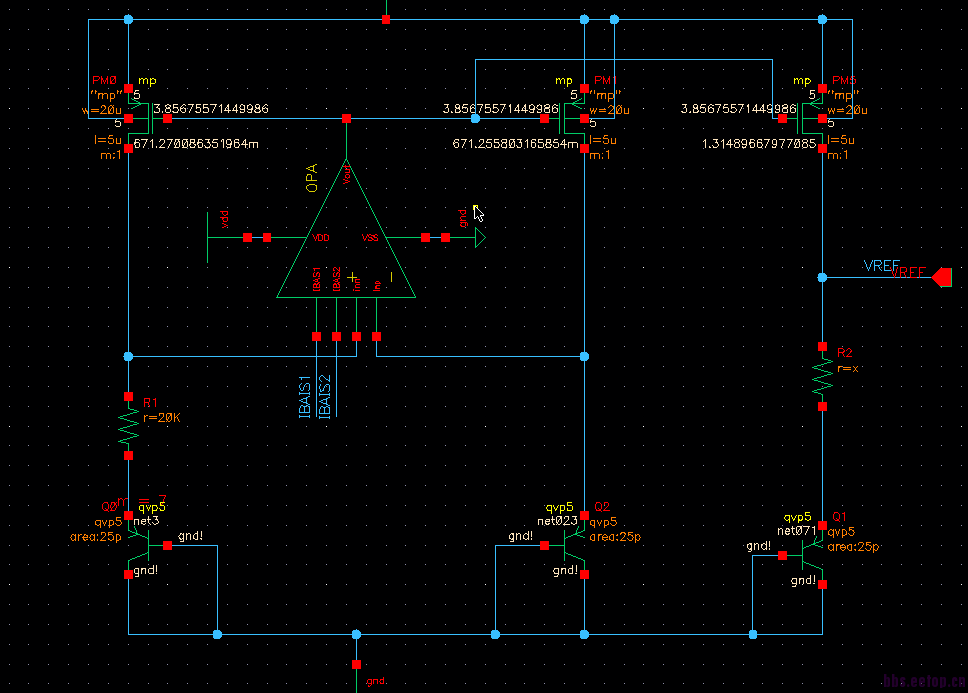

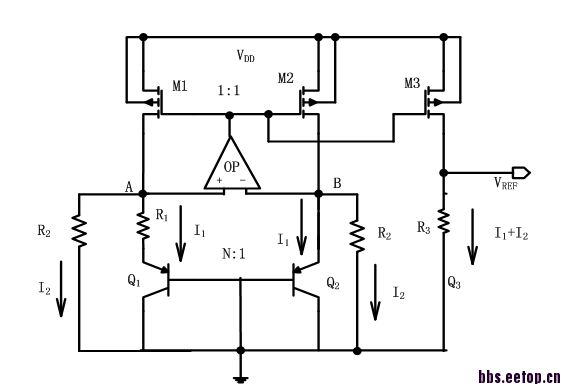

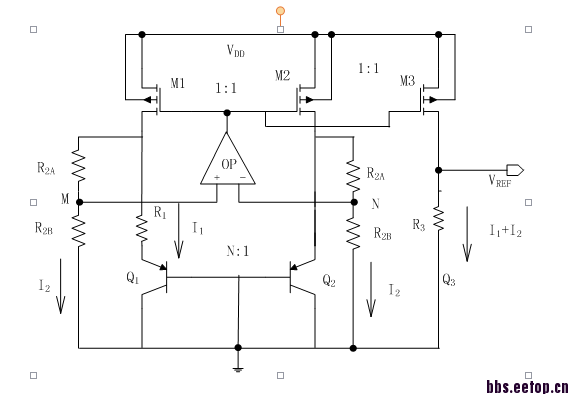

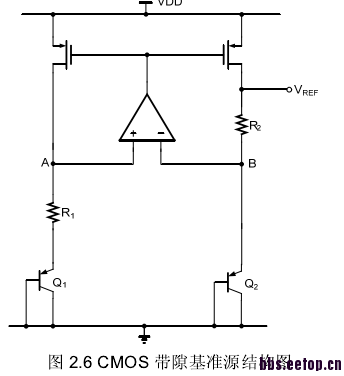

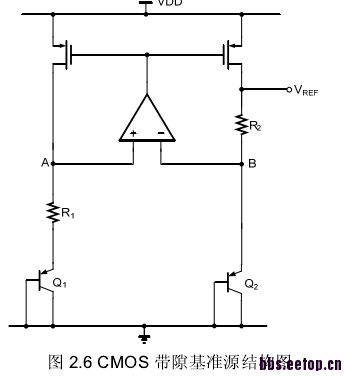

看论文时好多人用到图1、图2结构的bandgap,与书上经典bandgap的电路结构(图3)相比这里多了几个电阻和少了一个三极管,我想问的是

(1)图1多了2个电阻和图2多了4个电阻有什么作用,与图3相比有什么区别?

(2)图1和图2这两种结构的电路于什么区别?

希望给位前辈指点一下,小生感激不尽!

这个是因为你的运放的共模输入电压处在了ICMR之外的原因,你用了NMOS做尾电流源,又用NMOS做输入对管,那么你的ICMR下限就是VGSmn0+VDSmn2,在你电路工作时运放的共模电压低于这个值,那么输入对管自然就不会处在正常工作的饱和区,因此你需要把ICMR的下限拉低,不改变这个结构,不换PMOS输入对管也可以做到,只要调整NMOS的W/L使下限足够低也是可以的,当然这不容易做到。

如果换成PMOS管,则相当容易,ICMR下限甚至可以比GND还低,而且PMOS的噪声性能比NMOS更好,如果非要用NMOS,则像楼上说的换成折叠就可以了。

谢谢你的讲解。(1)图1多了2个电阻和图2多了4个电阻有什么作用,与图3相比有什么区别?

手算一下,不难发现图一图二的基准电压是可调的,图三是固定的

(2)图1和图2这两种结构的电路于什么区别?

四个电阻的情况,运放的共模更低,或许能用在低压设计?

另外,要注意图1图2的启动图3中由于R2的存在,可能会使得两个PMOS电流源输出有一定偏差,进而使得流过BJT的电流也会有一些偏差。而图1和图2应该解决了这个问题,而且图2中对于运放的输入共模电压会比图1的要低,有可能是降低功耗或者其他考虑。这三个图都可以调节电阻比,使得N的取值不至于太大,但是前两个图效果会更好一些,代价是器件成本上升

谢谢小编的详细讲解,前面两个问题我都懂了。另外,要注意图1图2的启动?

这个能将详细点吗,能给个电路图吗?那几个电阻主要是提高PSR的,另外也提高了电路的启动速度。

你能解释一下为什么这种电路需要启动电路吗,找了一些资料说的好含糊。圖一,圖二是current mode ,好處是輸出可隨意不用一定在bandgap 約1.24v

圖二是為了 op較好在低壓的設計

圖三是voltage mode精簡版,缺點是pmos受vds之差異造成不準確度

因为电路两边分别为线性和非线性电路,导致电路存在两个简并点,若没有启动电路,电路可能稳定在0电流状态。问一句,你后来提到的图一图二中的Q3是不是省略了?还是说,你R2是个负温度系数电阻,得到的I1+I2本身就是与温度无关的电流呢?又或者是你负温度系数的抵消,靠得是R2和R3的综合作用?比如说图一。

两路bjt没有导通时,比如图二的运放输入都稳定在0.3v,电流关系也成立

也就是说有多简并点。

启动电路要确保启动到正确状态。

我印象中记得有人碰到过这种情况。申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。