bandgap相位裕度仿真结果疑问,请高手释疑

bandgap相位裕度仿真结果疑问,请高手释疑

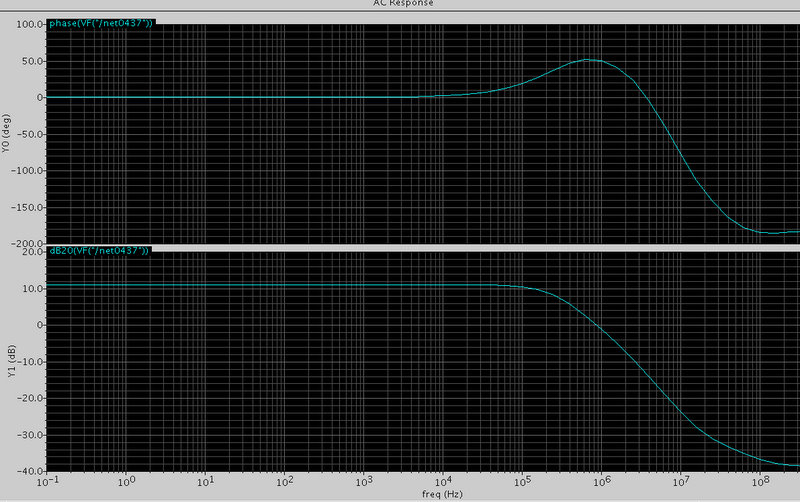

bandgap相位裕度仿真结果疑问,请高手释疑如图bandgap相位裕度仿真结果中,相位曲线为什么会上翘呢,而且超过了0变成了正的。这种情况可能是什么原因造成的呢?为什么一些书上都没有见到过类似的情况。

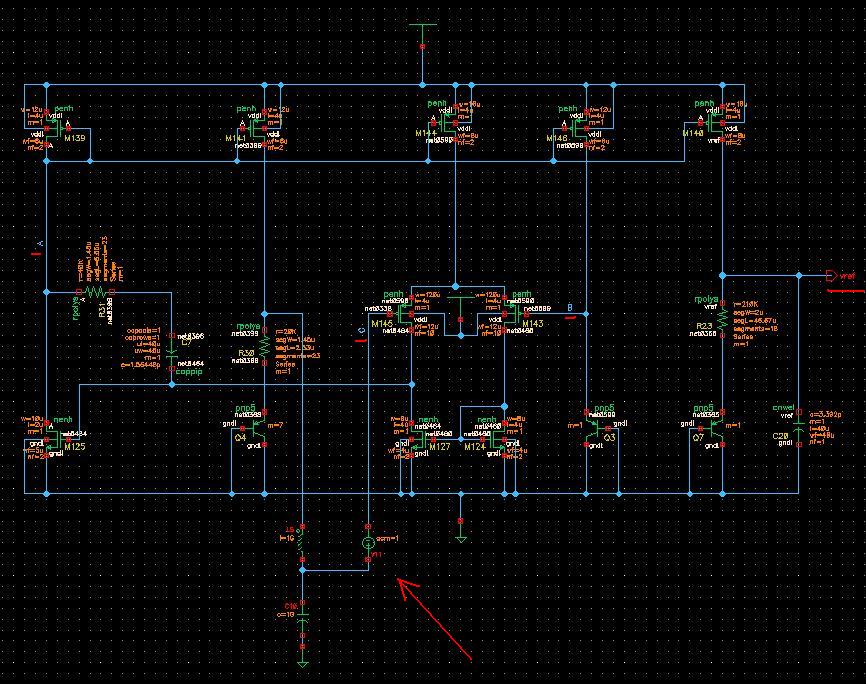

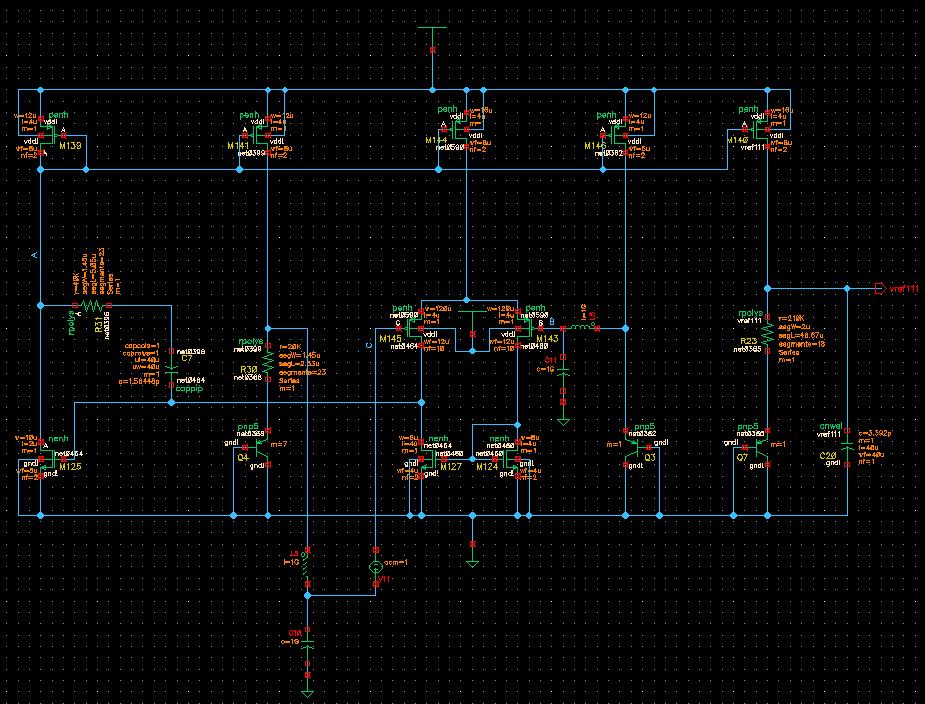

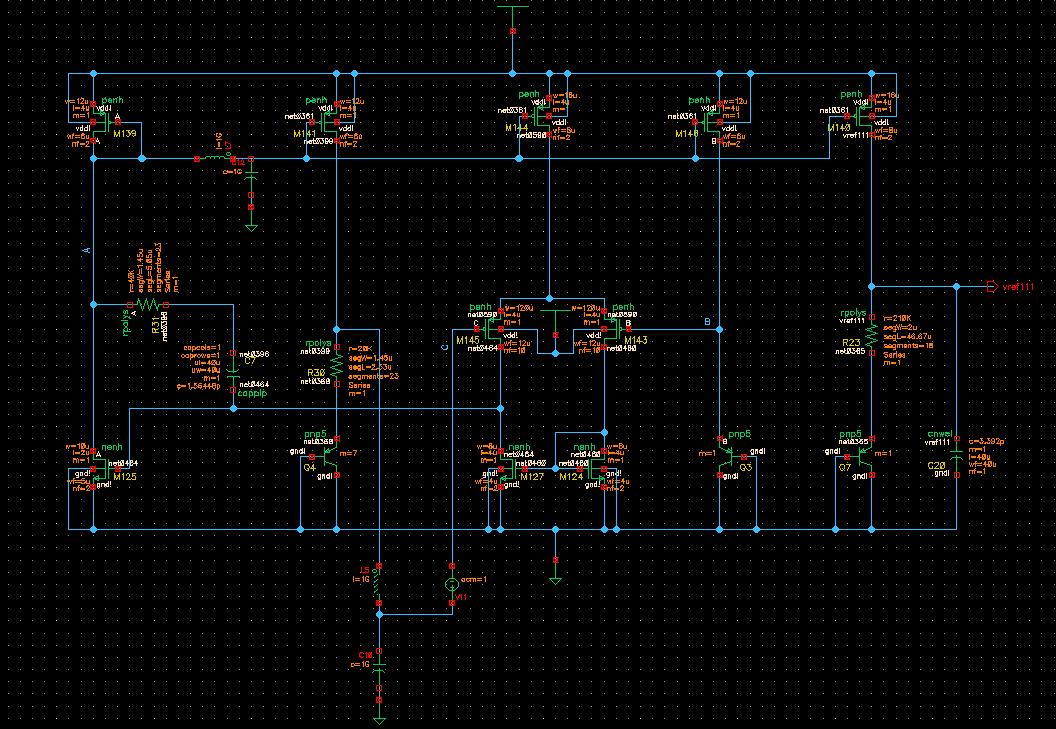

是不是我的带隙AC仿真方法不对呢?如图所示,这样加入噪声是不是可以,应该查看A,B,C,VREF这4个点中的哪个点来观察稳定性呢?

这种情况可能是什么原因造成的呢?为什么一些书上都没有见到过类似的情况,请高手释疑,感激不尽

B点是正反馈,C点是负反馈。你只断一点是不行的。

考虑断开M139送出去的Pgate。记得给M139这边加上模拟右边pmos 栅电容的电容。

或者你B,C都AC断开。用VF("/B")-VF("/C")来看AC特性输出应该看A点还是VREF点呢?

环路增益么,就是绕一圈。输出就是看你断开的地方

这位大哥,我图中断开线路的方法对不对,是要完全物理断开还是隔断交流就行了?还有是在交流信号加入的地方隔断吗?

断开方法对,就是这样的。

是在那里加。是这样断开,来看VF("/C")吗?

图是正确的。

两个断开点的vf的差值,就是AC结果。这样断有可能出问题啊。是由于自偏置电路也构成正反馈环路,而这个环路没有断开。

建议还是从M139那里断开是这样吗?在A点断开,然后用 AC Magnitude & Phase看A点,得到的就是这个带隙的相位裕度吗?

电路里的A点没东西啊?

在现在的电路基础上,你左上放的那个AC断开是对的。激励加载AC断开点的右面;看AC断开点左面的AC Magnitude & Phase。

在AC断开左面加上一个电容,电容的容值大概等于右面那几个pmos的栅等效电容。

C点的那些东西都删掉,不需要断开AC和激励这个电路本身就有点问题

运放的偏置是由运放的输出决定的,

这样环路就很复杂。

成熟的工程师应该不会设计这样的电路吧,。

而且上面的断开方式都不对的此话怎么讲?

------------------

通常的环路有两个,一个是正反馈,一个是负反馈,

但是这个电路就不止。

从运放的偏置电压到运放的第一级输出有两条通路,

运放的第一级输出到运放的偏置也有放大通路,

可以说这也是两个环路,

这样的设计都是安全隐患。

偏置电路还是不能省的

而且上面的断开方法,都无法查看这两个环路的增益和相位裕量。

断开点不对!

你可以试着分别断开运放的两个输入点做仿真,结果是不一样的!

应该断开运放输出常规设计都是自偏置吧, 省掉电流源。自偏置电路一般加个正反馈启动电路除去零态。稳定性ac仿真断开op输入(两端都断),断开输出都可以。老大推荐的方法是仿transient, 在环路中加不同的阶跃信号(改变阶跃幅度和阶跃)。

认真回答推一个

B C点是正反馈还是负反馈是怎样看的啊?

我这个菜鸟,理解怎么看正反馈和负反馈了,吼一声

建议用iprobe加入环路仿真stb,就不存在选哪儿断开的问题了。另外,加L、C仿真的方法是有条件限制的。

个人认为 利用叠加法比较可行在M139和M141之间断开

mark,学习中

电路零点的影响吧 EE240里面讲过

对,考虑正负两个环路,应该是在放大器输出端断开

学习了

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。