Bandgap中偏置电路的环路增益计算及稳定性的疑问

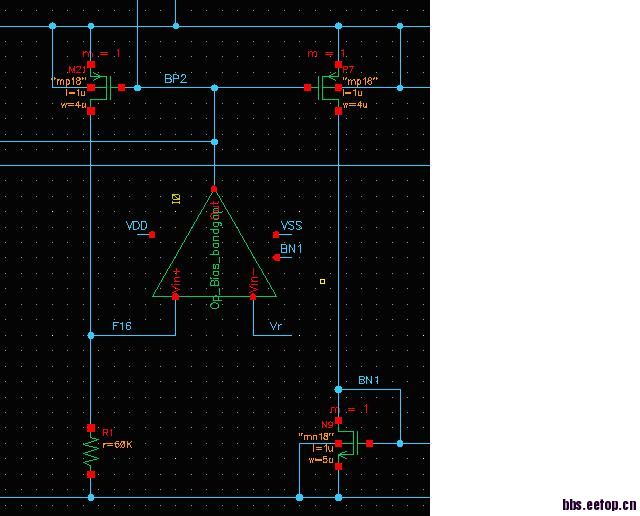

如图是带隙电路中运放的偏置电路。

图中,运放负端接Vref(稳定的带隙输出1.197V),

通过负反馈使IR1的电流变成与温度无关的电流,

最后将这个电流引出去作电流源使用。

这个电流源最终给两个运放提供电流偏置。

一个是本运放中NMOS管电流源

还有就是Bandgap中运放的电流源

图中本运放的电流源的偏置BN1也由IR1来提供。

Q1:这里反馈如何计算?是算电压-电流型的,还是电压电压型的。

我个人认为最终取的是电流,应该是电压-电流型的。可输出的是BP2的电压,这个我该如何理解?

两种方式的环路增益如下:

设运放的直流增益为A。

a:输入为Vr,输出为IR1。

F16处断开ac回路,在R1处并联一测试电流,取Im21的值

环路增益af=R1*A*gm(m21)

b:输入为Vr,输出为Vbp2

BP2处断开ac回路,并在M21的G端添加一测试电压,取运放I0的输出电压

环路增益af=gm(m21)*(rdsm21||R1)*A

Q2:环路增益我该算哪条回路?

测试回路:

1.断开Vr的ac回路,即输入ac置零。

但是环路中还存在一条回路,就是由测试信号最终传至Vbn1处的小信号,bn1接运放的尾电流。

如果我不将BN1的ac断掉,af的值会高于原值。

我是否该将BN1的小信号断开?

如果断开,环路稳定的条件是af=1时,phase margin(af)> 60

如果不断开BN1,这时af=1时,phase margin(af)<60,还需将PX内推,或减小af

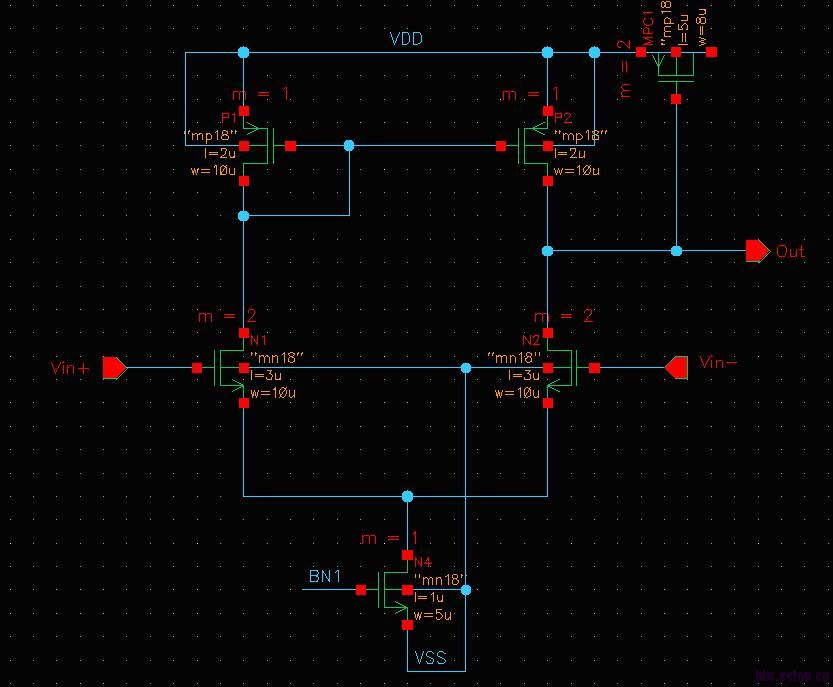

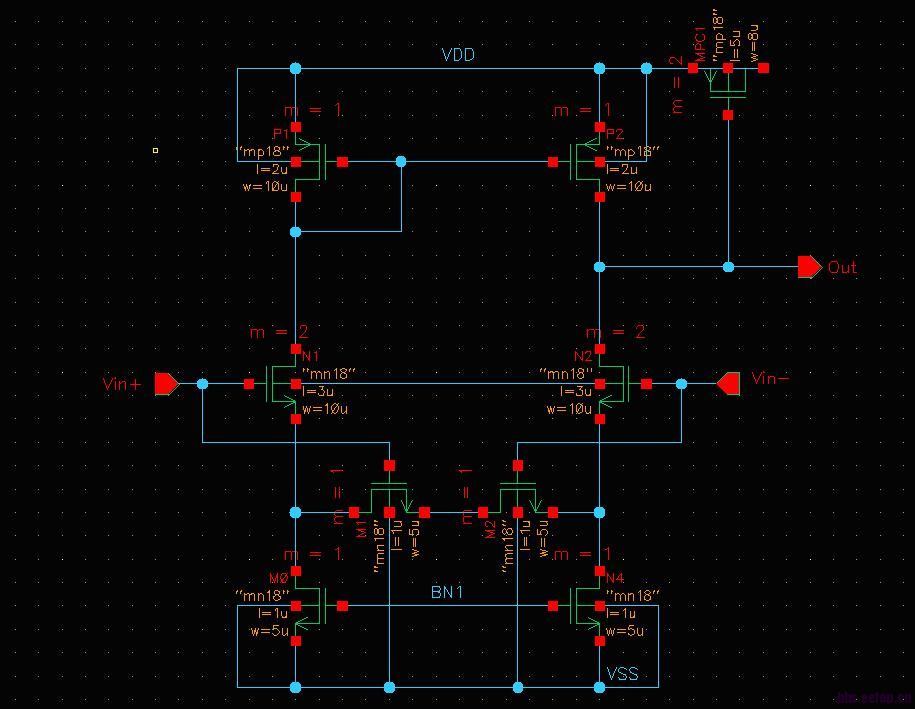

Q3:实际仿真中使用OP1的结构,始终无法满足phase margin的条件,于是采用OP2中的结构,

这个结构是原电路的结构,OP1的结构下A=258左右,OP2的结构下A=40左右。

请问OP2的结构,增益公式该如何表达?极点如何推出?

请高手指教,谢谢!

Q3, OP2的增益=gm2 *(ro(N2)||ro(P2))?

OP1的,OP2的我不知道该怎么算?

能告诉我OP2的增益和零极点怎么算吗?

还有就是这个电路怎样才算稳定,应该按照哪种类型的反馈来计算?

BN1这条支路该如何处理?

谢谢!

有必要这么复杂吗?在运放的输出出加一个vdc,仿stb,假设你用cadence的话。

不好意思啊,我是新手。只是想理解这个环路的稳定性该怎么算。

仿真工具是Hspice,那个stb是什么意思?

谢谢!

stb就是仿真环路增益的

你是说cadence spectre吗?

手头只有hspice的,能告诉我这个环路增益应该只仿一条环路还是BN1那条也算上?

Hspice就不知道有没有类似的了。

算的话,基本上有两个反馈环路,一个正反馈,一个负反馈。设计要求负反馈的增益大于正反馈的增益,环路才能稳定。运放可以设计为2级,环路主极点放在miller电容处。

学习了

我可以理解成:断开输入的ac信号。在反馈网络出加测试信号,测量正反馈与负反馈同时作用下的输出信号。最后看这个信号的PM是否足够。这样就可以了嘛?

如果有多条反馈通路,是不是都可以这样测量呢?

那条负反馈我该如何理解?输出是电流还是电压呢?我觉得是电流,但无法理解输出却是VBP2.虽然gm*VBP2又变成电流了。

另外OP2的增益与频率表达式该如何表达?

谢谢!

回复 3# chenchenbeyond

我是觉得,op2中M1和M2是开关管,导通的话,OP2就是简单的差分放大器了。

不知道这样理解对不对。

OP2的增益问题已搞定,那两个开关管在深线性区,通过调节尺寸可以调节它们的rds。把他看成带源级负反馈下面的电阻。

这样调rds就能把运放的增益降到需要的值。

我同样还有疑问,就是这个环路的建立时间怎么算?

Vout(t)=Vstep(1-e^(-wt))

我这里按电流反馈来算,怎么去从建立时间来推他的GBW?

谢谢!

thank

mark,学习中

太高深了,学习

我主要针对的是工艺偏差,而失调是芯片内部不对称不匹配引起

我指的工艺偏差是指大批量产时,芯片于芯片间的离散程度

主要是因为

(1)同一个wafer上不同位置的die

(2)同一批次中不同wafer上die

(3)不同批次中的die

工艺稳定会影响bandgap的初始精度

这方面主要关系到器件参数

(1)电阻绝对值的精度 约+/- 20%

(2)pn结电压等

这些其实受工艺决定,比如doping density ,the depth of difussion,

doping profile 等

学习了

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:LDO负载调整率的问题

下一篇:bandgap相位裕度仿真结果疑问,请高手释疑