LDO负载调整率的问题

录入:edatop.com 阅读:

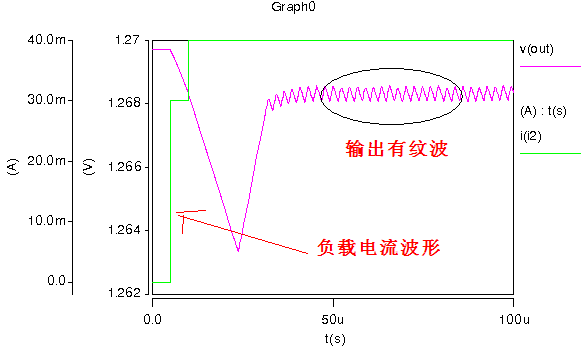

如上图所示,负载从0ma变化到30ma,再从30ma变化到40ma,LDO输出出现震荡,请问大大门是哪个地方设计出现问题?

在仿真的时候,如果从0到100ma,输出波形是没有振荡的,但是从0到30ma的时候就会出现振荡,请问又是什么原因引起的呢?

求教,谢谢各位大大门~

0ma负载下的phase margin会不会不够?

30mA的相位margin够吗? 可以单独看看啊,感觉不够

3# rfzheng

谢谢回答~

请问如何通过仿真看相位裕度?

断开环,然后加一个ac?

zero's frequency too high , please move to lower frequency

Check the phase margin at all load conditions (from 0 to 100mA) because the PM changes with loads.

很显然,I=30mA时,phase margin不够!

6# yeoks99

如何check?是通过选取其中的几个点跑tran么?然后看输出是否ripple?

检查在30mA到40mA的环路稳定性,估计在这个范围环路的稳定性有问题。

你有试过开环测.AC吗?

.AC可以测phase margin

thanks

可以用stb看

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。