Calibre LVS结果中的ERC pathchk Polygons Database

录入:edatop.com 阅读:

Hi!

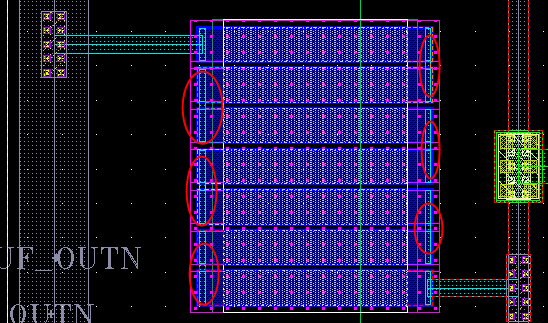

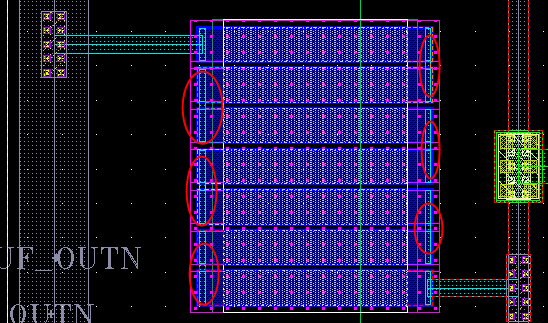

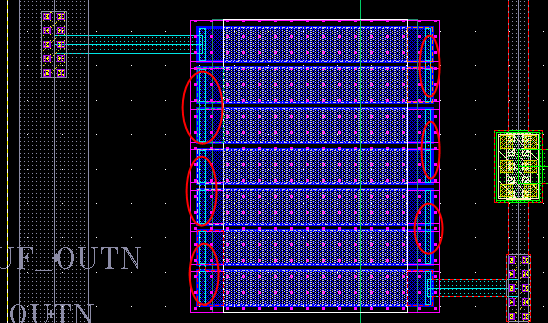

在对一个电路做LVS后,“comparison results”显示的是correct,但是“ERC pathchk Polygons Database”中显示ERC错误“check ERC PATHCHK! LABELED NOFLOAT 14”,定位是在版图上的电阻栅附近,如下图所示,是个偏置电阻。

为什么会报这个错误呢?如何消除这个报错?

在对一个电路做LVS后,“comparison results”显示的是correct,但是“ERC pathchk Polygons Database”中显示ERC错误“check ERC PATHCHK! LABELED NOFLOAT 14”,定位是在版图上的电阻栅附近,如下图所示,是个偏置电阻。

为什么会报这个错误呢?如何消除这个报错?

也想知道这个原因,希望大家解答

没人知道?

最近也被这个问题困扰~

我猜應該是跟 LVS REDUCE SERIES RESISTORS YES 這個default設定有關~

因為簡化了電阻,他之間的接線就被認為是floating~

我也遇到你这样的问题了。请问你最后是怎么解决的呢? 这是个什么物理原理的错误呢?

求解?

老版本的calibre 没有这个问题,calire 2012就会报这个错,求解

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:共模反馈环路的稳定性分析探讨:环路带宽和环路裕度

下一篇:cadence 加库不对咋回事啊在线求解答啊下午交报告了