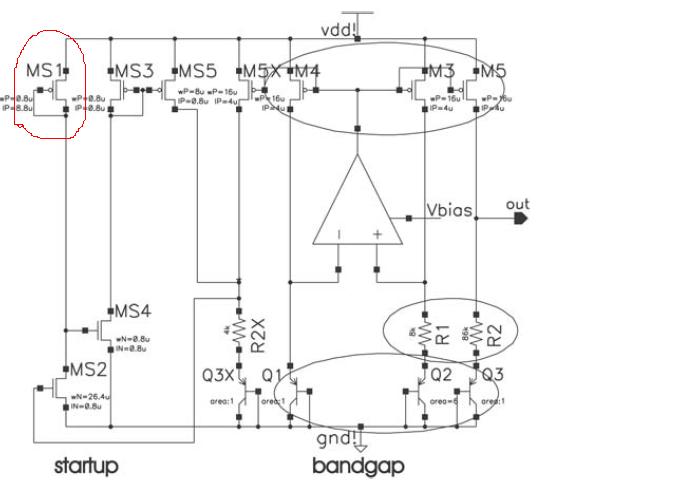

恳请大家分析下图:一个完整的带隙基准电路图中的一些问题交流请教

这个WL值一反常见的W>L的特点,反而是W<<L。

除了形成电阻值大对电流构成影响外,这种取值的主要目的是?

另外 layout应该怎么实现好呢?

Q3X在这里的主要作用是?

当bandgap正常工作, r2x的上端会产生一个较精确的参考电压(个人认为电流一定的话bjt上的压降比电阻上的精准),这个电压加在ms2这个nmos上,产生的电流流过ms1,一定要使ms4截至, ms1的阻值要大些, layout随便,最好w大些。 我在其它bandgap的启动电路里见过这种倒比管,作用类似。

电路是不是画错了?启动电路无法启动bandgap啊

当通以vdd时,电路可能稳定在0状态,所以需要启动电路。

可以这样分析:0状态时,所有的nmos管G级都为0,所有的pmos管G级都为vdd。这样MS4的G极电压为vdd,MS4

管导通,提供电流给MS3,MS5复制MS3电流,这样R2X电压升高,电压离开0稳态,进入正常工作状态。此时,R2X电压的升高使得MS2导通,这样MS4得G级电压降低,使得MS4截止。

图看不大清楚,MS2的W/L应该比较大,类似于一个小电阻,MS1是个倒比管,是个大电阻,这样电压分配在MS4的G级电压可以很小,使得电路正常工作时,STARTUP CIRCUIT 关断。

/ k+ k# G$ \* h2 {6 b i

这个电路是IEEE的,应该没有错误。

sean_4413:

可以这样分析:0状态时,所有的nmos管G级都为0,所有的pmos管G级都为vdd。这样MS4的G极电压为vdd,

前面半句可以理解。后面半句很疑惑?

根据电路连接特点:应该是所有PMOS的S/B级都连接到VDD的,所以是VDD。 G级怎么是VDD?

另外 guang3000认为 MS1最好w大些,但是IEEE的作者却取的是这个电路里面的最小值,W=0.8. 不知你怎么解释?

还有一个问题:一个工艺上的问题:

0.18UM某工艺里面的MOS模型有nch,pch,nmos_rf,pmos_rf等。 RF MOS模型nmos_rf,pmos_rf的尺寸不知为什么限制得的很小,W宽度限制在1.8~8um;而nch,pch的宽度W则是0.22~900um。

在设计LC VCO及其他附属AFC电路包括数字部分的时候,很明显,要用到射频电感模型,varator,MIM等。

我的问题是: MOS应该选择那种模型呢?

选择baseband device model:nch pch还是RF device model:nmos_rf,pmos_rf?

因为 这里除了VCO以外还有其他的数字部分。

模型库同时提供两种大的类型的MOS模型,是否表示可以同时在一个片上实现?

对于射频工艺了解较少,谢谢。

貌似bias是由最左边的支路提供的,不然启动电路没用啊,而且有bias的话也就用不着启动了,自偏置才要启动

MS2的W/L应该比较大,类似于一个小电阻

MS2的W/L应该比较大,类似于一个小电阻

MS2的W/L应该比较大,类似于一个小电阻

为什么我是无法查看呢

MS2是26.4um 和0.8um

图上可以看出

和大家想的一样,确实比较大

paper上很可能省略一些东西的

稳妥起见还是有个自偏执好点

香港科大的philip有一篇相似的bandgap设计

就是有ibias的

这有什么不行的

我就是这样理解的呀,开始时MS2是断开的,MS1却是有源的电阻的连接形式,所以是导通的,这样MS4 的G就会是高电平,所以会有电流流过,从而启动电路

运放已经有外界偏置了,M5X自然而然的流过PTAT电流,用的着启动吗,这个电路图肯定是不完整的,偏置是自偏置才需要启动。

这样理解不正确。左边的是启动电路。上电时,由于二极管的作用,左下角管子截止,电路启动成功。电路进入正常状态时,左下角管子导通,启动电路关断,电路正常工作。

你仔细看看我的留言,如果看懂了,我觉得更容易理解启动电路了,我的很直观的

ding yi ge ba

启动完成后,启动电路就不该对主电路产生影响,所以我估计Q3X目的就是认为多加一个BE压降,提高左下管的VGS,进一步保证该管的负载仍为MS1时,VDS足够小,从而保证启动电路不对主电路产生影响

就算是运放已经有偏置,Bandgap基准就不用启动电路了吗,有什么依据呢

我是这样理解的:运放工作了,两输入端的电位仍可能是零,或者说输出端(即M4的G)仍可能为高,所以仍不能保证BGR可以启动

严重同意!

仿真不一定会出来,但是实际上测试的时候会出问题。

期待...

Answer your questions

Please visit the following website

http://www.eetop.cn/bbs/thread-190594-1-1.html

一个bandgap启动电路上,漏栅短接的红色PMOS的参数是W=0.8;L=8.8。7 n% @/ l. U3 M- Z+ M( \

Q1: 这个WL值一反常见的W>L的特点,反而是W<<L。除了形成电阻值大对电流构成影响外,这种取值的主要目的是?! }; V+ ^) H# U4 k& _

A1: L>>W is correct. Please see Johns & Martin’s “Analog Integrated Circuit Design”, pp 250, Figure 6.2’s Q18. The purpose of this PMOS is to forma a large resistor and always turn on.

Q2: 另外 layout应该怎么实现好呢?

A2:

Q3: Q3X在这里的主要作用是?

A3: Dummy for matching

Q4: 我的问题是: MOS应该选择那种模型呢?9 ?7 G2 @! [! l: Q8 V选择baseband device model:nch pch还是RF device model:nmos_rf,pmos_rf?

A4: MOS应该选择pch or pch3

MS2的W/L应该比较大,类似于一个小电阻

QX3的作用应该是个高阶的温度补偿吧

至于前面所说,在零状态时,所有的PMOS的G都是VDD ,这应该是零稳态的一种初始状态吧,不然的话初始状态时所有的PMOS的G都是0,那就不需要启动电路了

该启动电路貌似无法启动

电路有误?

今天再仔细看了下,图上标明的启动电路根本和核心电路部分无关,不会起启动作用。

也来学习了!

何时才能成为高手阿

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:请教LDO设计时的负载问题

下一篇:如何设定LDO指标?