求助!sigma-delta ADC VerilogA 仿真问题

录入:edatop.com 阅读:

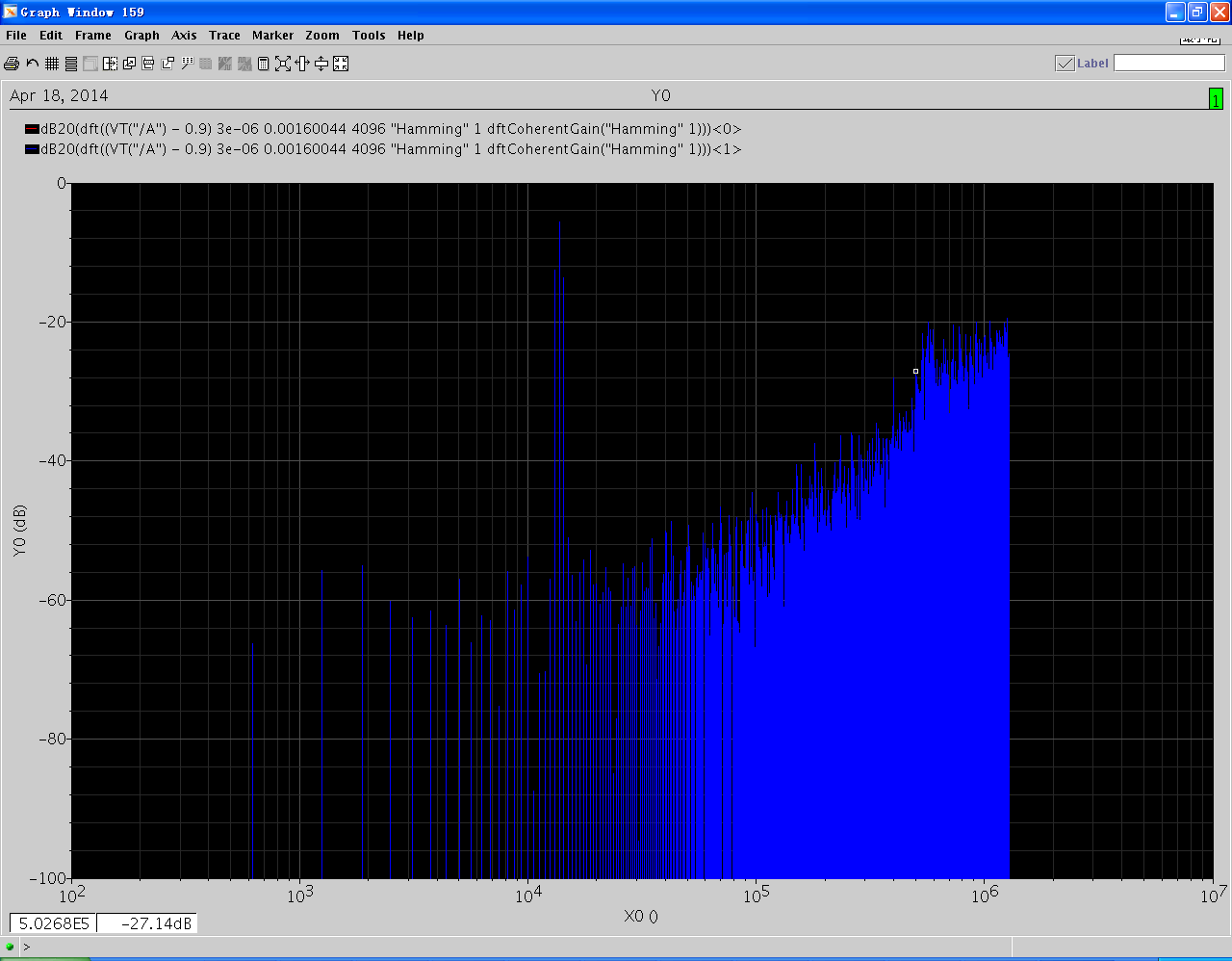

求助关于sigma-delta ADC的VerilogA系统仿真,输出在Cadence中进行频谱分析后结果如下图所示,

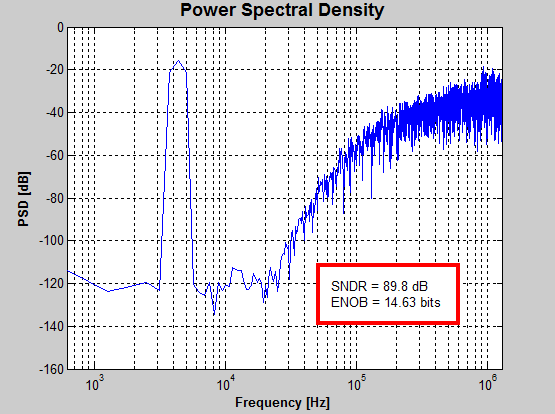

噪声很大,MATLAB仿真结果如下:

不知道为什么仿真结果SNR差别这么大,因为频谱趋势是正确的,会是时序的问题吗?请大家帮忙看下问题会是哪里呢?用的运放、比较器、开关都是理想的。

还有一个问题,反馈电容的值是如何根据积分电容和采样电容来确定呢?

行为级和veriloga,你可以比较一下是否完全一样,就知道直流哪里出来的。

向大家学习了

请问,第一幅图的结果是什么原因?

低频噪声大 是不是引入了dc

这个结果是因为我的信号频率有问题,信号有点泄露了。

采点和窗函数加的有问题吗?

请问下小编在cadence里面怎么进行频谱分析?是calculator里的psd吗?

您好,能给我发一份吗?邮箱 654833657@qq.com,一起分析一下,看看,谢谢。

您好,能给我发一份吗?一起分析看看。654833657@qq.com 邮箱

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:CDR的测试问题

下一篇:开关电容电路的反馈因子是怎么回事?