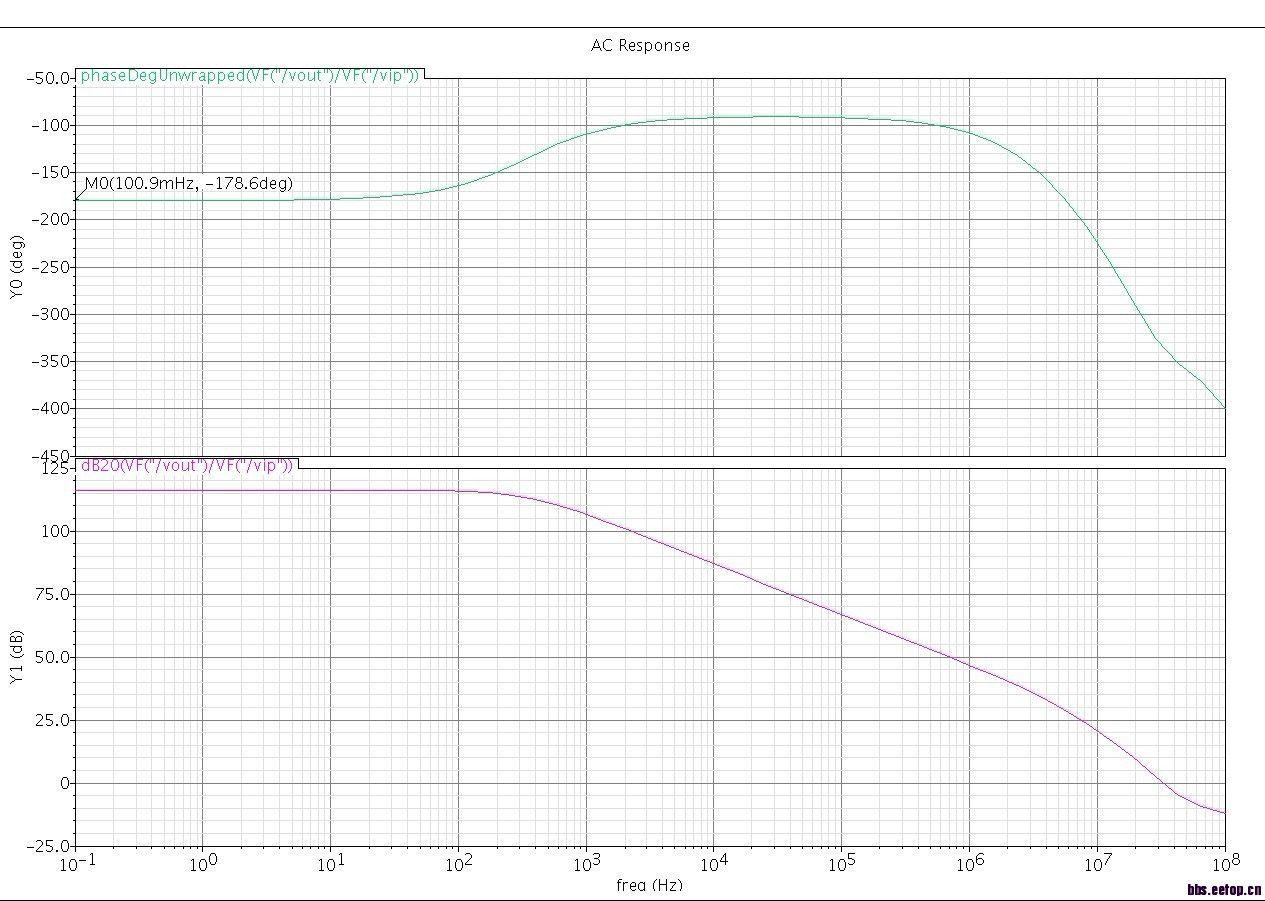

opa loop simulation(phase 曲线) class AB

在仿真opa时,出现 增益减小,相位增大的现象!(class AB opa)

请问这种情况是怎么引起的.

多谢!

求解......

看看trans怎么样

tran 没有看到振铃,一切很好啊!

请问这是 什么情况导致的?

求高手啊,我有的时候也会出现这种情况

zero

razavi书上讲过如果有两条路径的话可能就会出现zero

你能不能贴一下电路和testbench?

有时候testbench做的不对会这样

从曲线看,这是个正极点,这个就很奇怪了

你要把电路仔细的分析清楚,零极点位置都要在你的掌控之中

难道是内部反馈所致吗?

顶一把。

右半平面零点

no.....

anyone get this question , ever.

no....

...ding......

how to solve it ?!

顶,等着小编上图

这个问题,好几年前遇到过。当时用的是TSMC 0.25um的工艺,仿真的结果和你这个一样。

我当时怀疑是spice model的问题,找了很久,发现是由表征CMOS漏电参数的因子引起的,把其中的系数改成0,就正常了。

就这个问题和TSMC SPICE model组的人电话会议过很多次,最后,他们也确认这种现象是这个因子引起了。

但确实最后也没找到引起这种现象的确切的原因,猜测的可能就是,Floating bias的漏电引起了类似零点的作用。

tran,包括tapeout都是没有问题的,而且只有class AB类似的Floating bias的时候才会出现。

现在不怎么用TSMC的工艺了,不知他们现在的model是否还有此问题

以上仅供参考

左半平面零点会导致相位增加 增益下降

这个问题我也碰到了,我用的是smic18的工艺,也出现了这个问题,我去看看是不是工艺问题

请问一下你说的这个CMOS漏电参数因子 是什么参数,在哪里修改呢?

到底是什么原因引起的呢?

原因到底在哪里呢? 顶一下,这个问题不要沉啦

mark 以后可能会遇到

我也遇到这个问题了,STB有问题,但是tran ac都没问题。查看了,就是浮动电源造成的,但是没搞懂具体原因,求高手指导。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:国内高校模拟IC排名

下一篇:大家帮忙看看这个多级补偿电路