低压带隙基准的设计问题

录入:edatop.com 阅读:

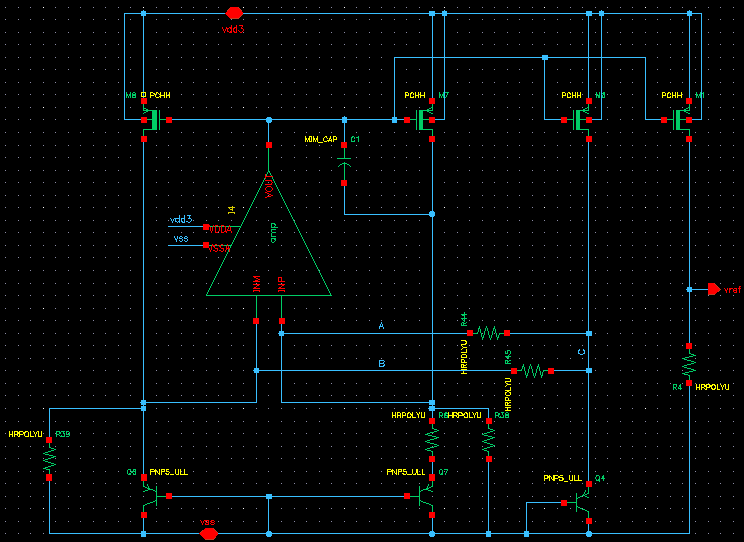

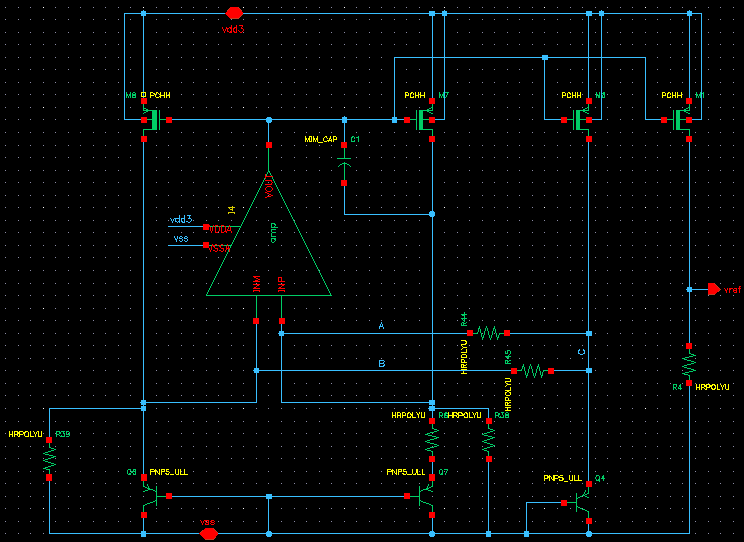

设计了一个输出0.55V的基准电压,电路结构如图,输出接了一个RC低通滤波器,做DC分析时没有一点问题,RC低通滤波后输出0.55V不变,可当我把电源电压设置成VPWL,0秒的时候0V,1p秒之后上电到1.2V,之后稳定在1.2V不变,然后去做了一个tran仿真,可此时RC低通滤波后输出电压只有0.25V了,我测了一下,此时RC低通滤波器的这个电阻R上竟然有电流,也就是说跟图中这最后一个输出电阻分流了导致基准输出电压减小,我继续测了一下,原来是tran仿真时,这个滤波电压C相当于短路,可电容怎么会短路呢,不可能啊,我低通滤波RC值分别为R=15K,C=1u,当我把C改为1PF的时候,就变正常输出0.55V了,有谁出现过这个情况吗?求解答!

原因很简单,你滤波电容太大,一直没有把电容充至0.55v。不过只要你仿真时间足够长也可以。

上升时间1ps太快了,设个us等级试试看

2楼正解。

1uF电容值太大了,直流仿真时电容相当于开路,电路不受影响,瞬态仿真时电容要充电很长时间,在保证交流稳定的前提下把仿真时间设置足够长的话或许能看到变成要得到的值吧。滤波器的R和C值不是随便设定的,要根据具体应用来设计。

看不懂,外行学习

R44和R45干什么用的?谢谢。这个电路启动比较困难吧,你怎么做启动电路的?

R44,R45可能是二阶补偿

对的,就是二阶补偿

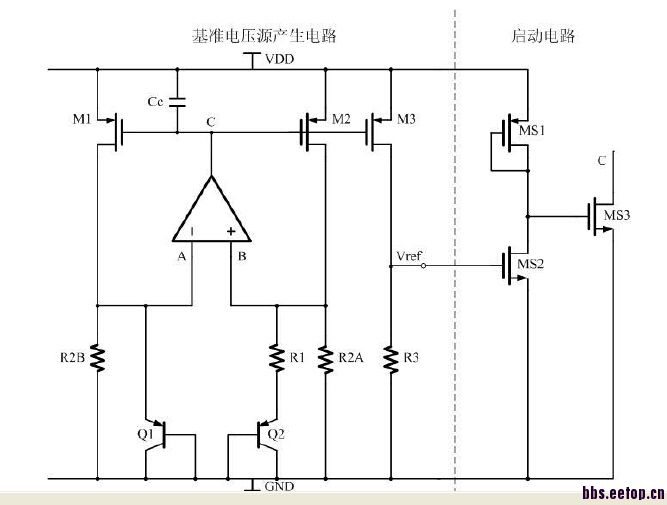

二阶补偿用的,这是我的启动电路,上图中没有给出来,如下图:

好像启动电路的margin总是很小

觉得这幅图比图一的结构要好一些

恕我学识不深,什么叫做启动电路的margin?这个真没听过

就是加了启动电路后BG什么时候启动什么时候不启动,离不能启动有多远,要量化这个问题

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:MOS管宽长由哪些因素确定

下一篇:PLL中PFD的相噪仿真的问题。