做CPPLL的进

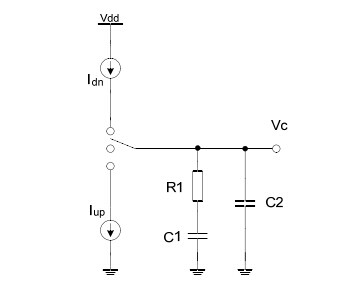

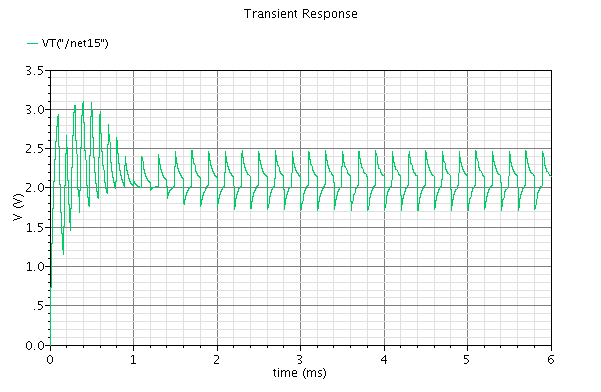

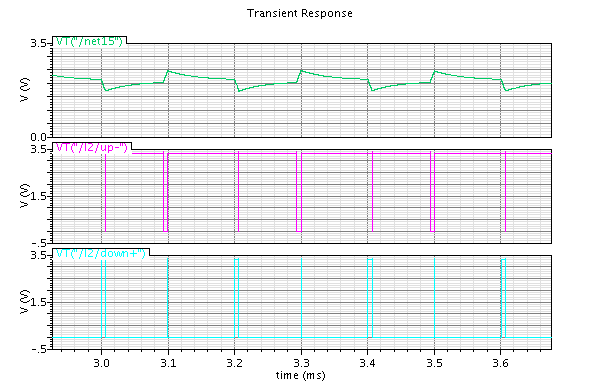

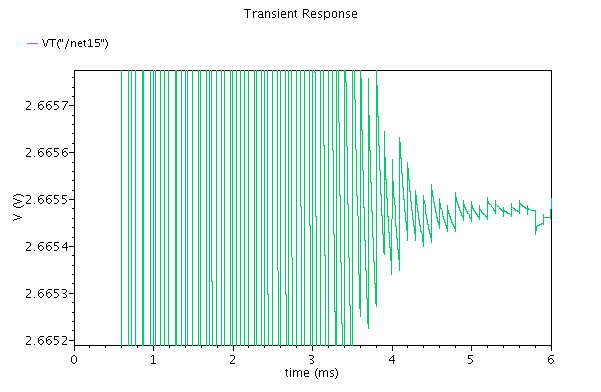

在做电荷泵锁相环仿真时发现低通滤波器输出电压的波形如图2所示,图3为局部放大图和PFD的输出信号;图1为低通滤波器电路图,如果把其中的C2去掉,仿真后的低通滤波器输出电压波形如图4所示,可以看出有毛刺但是平均电压是很平整的,C2大小是C1的十分之一。请问图2中的控制电压为何如此不平整?

顶啊顶啊

感觉像是环路带宽太宽了吧参考频率、环路带宽各是多少哦

还有,感觉电荷泵死区不小啊,PFD用的什么结构

你有没有再试一下三阶的环路滤波器?

感觉是mismatch大了

那可真不叫毛刺,,,

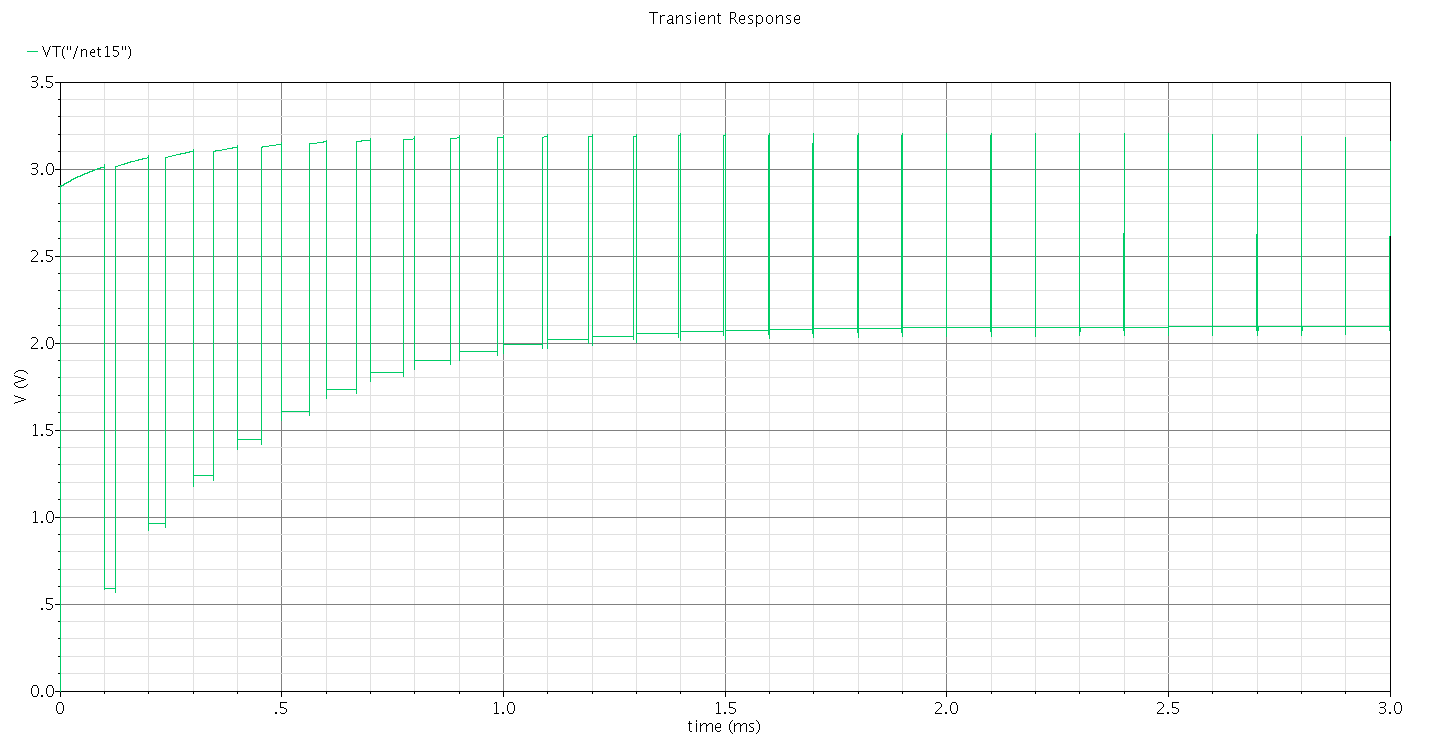

发现问题了,是电容C2太小导致的,现在把C2改为C1的三分之一大小,得到了如图5的结果,但放大后如图6,电压有uV级的波动,请问这个波动是如何来的?

发现问题了,是电容C2太小导致的,现在把C2改为C1的三分之一大小,得到了如图5的结果,但放大后如图6,电压有uV级的波动,请问这个波动是如何来的?

几微伏就很小了不过我记得C1,C2的关系是算出来的,3倍会不会存在不稳定的情况?

应该是带宽太大了。你找到的原因可能不是真正的原因。

电流多大,电容多大,零极点什么位置? 这些都需要算清楚了,再开始做。最后两张图看起来还可以

你根本没有解决问题,又或者你还根本不懂锁相环设计,好好研究拉扎维的书上关于锁相环的一章,多看论文。

C2竟然为C1的三分之一,太大了,一般至少十分之一左右才能保证环路的稳定性,为什们呢,书上写的很清楚,你这个问题我以前出现过,环路带宽太大,估计大于了参考输入频率的十分之一,导致系统不稳定,所以压控电压上才出现这种震荡,增加电容C1,C2,保持电容比b为10或者大于10

你的系统仿真稳定性过了吗?

同13楼

牛人辈出的年代

貌似Charge sharing 造成的問題. 電流關閉的時候, 電荷累積再 switch 內部的寄身電容裏頭.

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:mim capacitor

下一篇:最新消息华为计划逐年赶走30~40%的员工