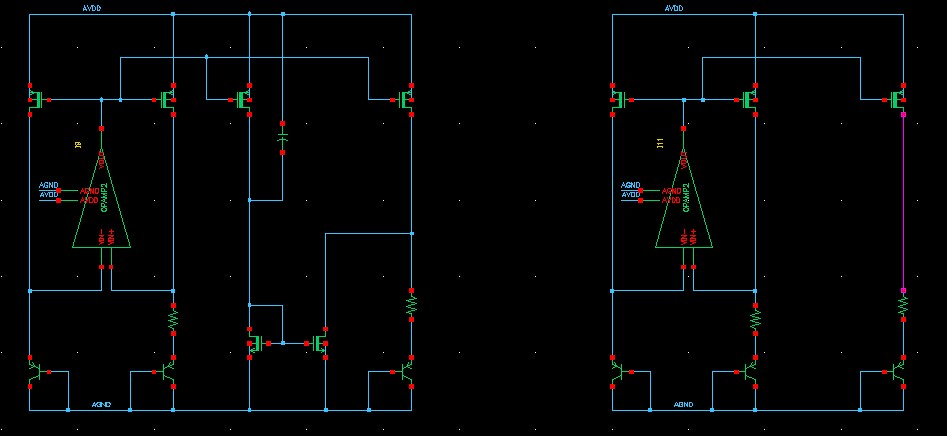

讨论一个带隙基准电路

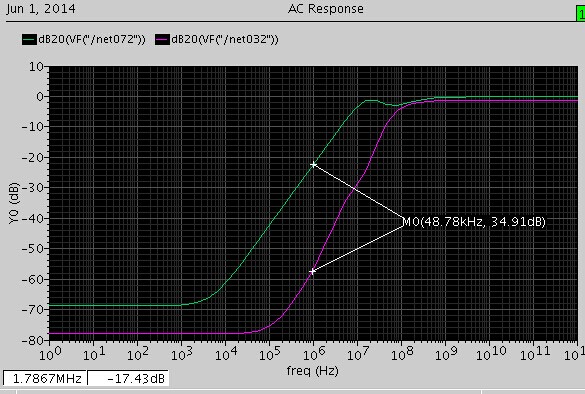

右边是个经典结构,里面是一个symmetric OTA,左边改进了一下,又引出了一路电流,经过NMOS电流镜镜像后输出,图中有一个电容,150fF,高频时,VDD噪声通过这个电容以及NMOS电流镜叠加到输出端,与原来PMOS管那一条支路上VDD高频噪声抵消,电容值选的恰当的话,高频PSRR会变好很多,1MHz时可以达到50db以上,这种想法实用不?

seeing

电流镜不分流么,会不会对原来PMOS输出的PTAT电流造成影响?输出端接的NMOS管是否也是PTAT级别的分流啊

貌似可行

下面电流镜镜像电流还是PPAT电流,他们之差还是PTAT

学习了

哈哈 你这个是不是只能部分消掉,不好完全消掉啊?

是的

corner角最坏情况也比经典结构高10dB,tt下高30dB

镜像的精度会不会有影响。特别是短沟道设计,镜像电流往往和被镜像的电流差很多

还有请问一下,带隙基准设计时,pnp管的面积怎么考虑?在工艺库中有2x2,5x5,10x10的三种标准pnp,请问设计时应该采用哪一个?从功耗考虑的话面积越小,电流越小,功耗越小,所以功耗限制下,选2x2的功耗最小,面积也最小。从其他方面怎么考虑?实际设计时应该采用哪个尺寸的pnp?请指点,谢谢。

我不是很懂带隙基准,我们以前弄的是5×5的

顶一个,急。

快流片了?这个两条路径抵消的方法不太实用。在保证稳定的情况改为cascode电流镜会增加PSRR,或者试试下面这个方法,电流镜镜像一路出来为输出加个cascode偏置,这样也能一定程度上改善。

怎么可能流片,呵呵,随便想出来的东西,cascode结构以前就有了啊,不算新结构

我就是想问一下这种结构以前有没有,如果兄弟们说都没怎么见过,而且有点实用性的话,就可以弄一篇垃圾专利了

个人觉得 ,小编的电路有一个问题,高频的时候,在电容处多了一路额外的电流,这个电流既不是正温度的,也不是负温度的,这样的电流叠加到基准输出电流,使得基准的温度特性反而差了,因为原来的电路的意思是正温度电流+VBe来产生基准。

只是根据电流大小选择不同发射极面积的三极管吧,并且注意下β,不要影响自己的电路精度。

推导了一下,感觉还是有效果的,应该产生了一个零极点对,其中的零点通过设置参数可以设置的比较低,从而补偿了输出节点的极点,而另外产生的极点处于高频,所以你看到psrr会变好。

温度特性是与频率没关系啊

昨天我推导了一下,我把所有的电容电阻都考虑进去了,眼睁睁地看着计算结果,化简不开!

NMOS只是镜像的作用,最后输出的电流是两路PTAT电流之差,还是PTAT电流!

小编的基准貌似精度不高哦

兄弟告诉我你怎么推的?我化简不过来

学习!小编好想法

看热闹来的吧哈哈

是向小编学习啦

你是ryc?

兄弟你倒是说句话啊,每次都是“see”,"mark"."good"之类的话。

额,不是= =

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:关于士兰微去年推出的SC3M70,谁知道情况?

下一篇:小数锁相环中数字delta-sigma调制器的输入位数能不能可变?