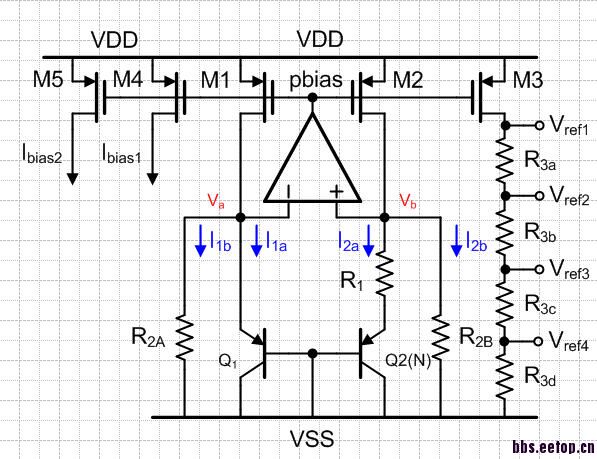

用banba结构做了个芯片,但是流片出来有问题,求教

banba结构做的ref,低压工艺,当VIN接近ABS电压时,EN on,发现ref会偏高20%,但是把VIN拉低一点点,ref又正常了,此时保持EN ON 的状态,把VIN再拉高,发现ref都没有问题。只有VIN 高,并且EN ON之后才会有问题,但是如果ref没问题,vin再怎么高也不会有问题了。有做过的请赐教,已然快崩溃了。

没看懂,VIN是哪个?ABS又是啥?EN在哪里?

你说的电压这上面都没有啊,请把详细的电路附上啊,我们之前做的就是这种结构,你们的运放是否也是用的耗尽想管子啊?》

低压下启动电路有问题,或者低压启动后某些节点漏电(这个也是启动有关)。

VIN 应该是VDD, ABS电压应该是absolutely电压

要查一下启动电路,高压的时候l衬底eakage会变大

ABS电压的含义?如果是保持EN on,VIN从0慢慢升到比ABS电压高得多的位置,再慢慢降到0,在这个ABS电压附近,VREF会否出现滞回的现象啊?就是上升到这个电压时,VREF比正常值高,但是后来再降到这个电压时就正常了。

VIN就是VDD,ABS是工艺承受的最大电压,电路拿不出来。实在没办法。谢谢

ABS是工艺承受的最大电压。我做了probe,发现只要EN on之后,VIN怎么拉升ref都不会有问题。只有在vin先建立,EN再on才会出现问题。

问题是只有VIN先建立到ABS电压附近,然后再EN on才会出现问题。而vin和EN一起增加,就算超过ABS,也不会出现问题。如果出现问题,VIN下降大概0.1V,ref就正常了,这时候你再拉升VIN,就算超过ABS很多,都不会有问题。

电路拿不出来,管控太严……谢谢您的回复。

牛!两点回复的帖子?我是实在睡不着了,起的这么早。

你按照你的测试条件仿下电路看看会不会有同样问题

小编的描述已经说明了这个电路有两个偏置点

有两个可能,

1就是某些器件在接近ABS电压的时候特性有些变化,产生了简并点

看一楼电路上的管子,如果VDD升到ABS电压,承受这个电压只有那一排PMOS管,而且PMOS管的VDS远小于ABS电压。建议小编留意下电路中那里有VGS特别大的MOS管,和那些承受电压接近ABS电压的器件

2 电路特性的变化,产生了简并点,例如楼上所说的启动电路,用上了VGS=VDD的倒比管做电阻等等。

VREF高20%,表明偏置电流大了20%。这个电路的其中两种启动方式一是将Va电压上拉,一是将pbias往下拉,无论是那种,都是最终将偏置电流变大的,觉得可以考虑改下启动电路的偏置,使得启动电路更容易关断,这样,有可能使得启动电路正常关闭的同时,更加偏离那个简并点

压力太大,睡不着啊。哈哈……其实不是的,我现在是美国时间。您有什么思路吗?

仿真在超过ABS+1V之后,低温-40时,看到里边提供的bias电流开始震荡,导致ref偏高了100%,但是不知道这个结果是否可信。

谢谢。现在做了个仿真,在vdd达到(ABS+1)V,t=-40,可以仿真到运放不稳定,会震荡,导致ref高了100%,但是不知道这个结果是否可信。至于你说的启动电路。我probe扎到启动的关键接点,直接将start-up电路关掉,发现问题依然存在。

应该还是启动电路的问题,这个结构启动电路不好弄,有风险

在PMOS电流镜和运放都正常的情况下,运放电压两边相等,理论上输出电压就被确定了。

这个芯片能直接精确测出uA级别的电流变化吗? 例如先测初始功耗,再测异常情况下的功耗(要考虑PMOS电流镜的电流+20%),

将这个功耗差减去PMOS电流镜20%的增加量,看是否会有电流过大或变小的情况。

可能运放工作不正常,导致输入两端的电压不一致。可以仿真下运放偏置电流过大或过小的情况,看输出会否升高。

运放的偏置电流源是拉扎维书上两PMOS,两NMOS+电阻的结构?

最后想问下是模拟工艺还是mix singal工艺啊,是线宽很小例如65nm的工艺吗?

bias电流开始震荡 ==> pbias to VDD 加一顆 5p ~ 10p 的電容。

start-up 可能有些問題,你方便從公司用手畫電路再貼上來嗎?

静态电流大概从100u增大到了140u。现在正在等待新的芯片probe。我做的是.35工艺的。

probe基本上排除了启动电路的问题,我觉得估计是这个震荡的问题,现在等待新的decap芯片做probe验证。出来结果会告诉大家的。

咱们又见面了,哈哈。电路实在不方便,因为这个芯片还没到市面销售。而且涉及公司机密,基本结构式没有问题的。VDD到gate加了7p电容,看起来还是不够,准备probe再加一点看看是否能fix这个问题。有进展会通知大家。不过我也只是猜测。

运放工作不正常,PMOS电流镜增加了20%,但是总的电流增加量为40u,多出来的一部分电流不知道跑那去了。

難怪覺得這個帳號很面熟啊....

下 .OP 時的 DC 工作點正常嗎?

一旦震荡起来电流可能失控了吧

你这个问题,我们在1.2V的相同结构的bandgap上碰到过类似的问题,低压上电没问题,高压上电bandagp震荡,输出电压偏离正确电压。分析看来就是bandgap自身的正负反馈环路和启动电路的大环路震荡的问题,根源可能来自于bandagp正负反馈的稳定性不够或者启动环路的稳定性不够,如果你的bandgap输出没有做大的滤波,看看是不是能偶观察到基准电压的是否存在两个振荡频率。

另外,如果可以的话,可以对比低压和高压下的电流信息。

我分析不是振荡的问题,否则En on以后改变VDD肯定可以看到电流电压变化的现象。我同意存在简并态的观点,就是由于En打开而造成的一种非设计目标的状态。这个最好做做后防,感觉同layout的结构有关。

这个结构不是很好,以后还是别用了。

主要就是启动问题,一个bandgap如果不能很好的启动,其他指标做的再好也没什么太大意义。

mark。

mark too....

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:Tow thomas filter 設計問題

下一篇:sar adc 电容失配