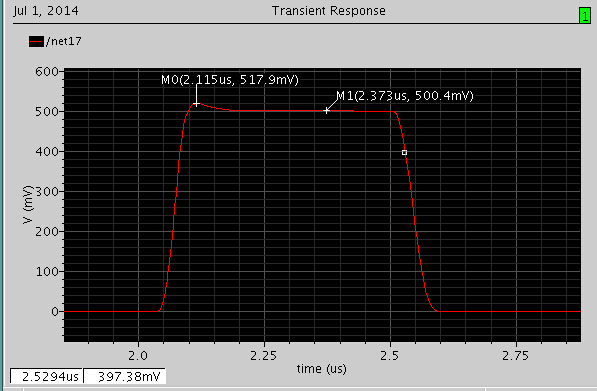

求问,关于震荡的原因

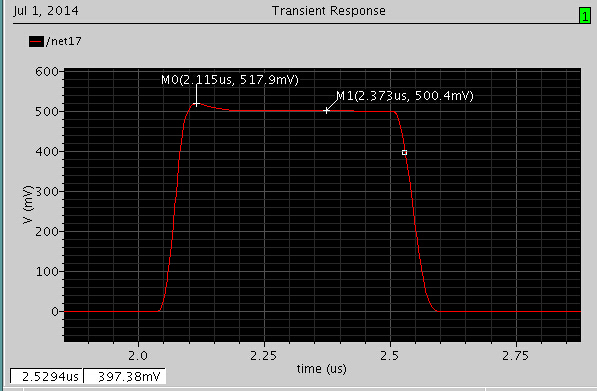

请问上面这两种震荡分别是由于什么原因引起的?为什么第二种是在相位裕度足够的情况下发生的?

楼上的同学,第二张图哪里震荡了?

第二张图,我的确不能说他震荡了,但是的确是凸起了,请问凸起的原因到底是什么引起的?我很困惑

关键是第二张图,求解,到底是什么原因引起的?

相位裕度再大点就不鼓包了

第二个图的相位裕度还是不够啊

根据你提供的波形,有一下几点疑问:

1 你的运放的输入输出都是rail to rail?

2 你的供电电源是单电源还是双电源?

3 你的闭环增益是多少?

4 你的仿真波形是基于前仿真还是后仿真给出的?

你的相位裕度为多少?60?80?90?

同时还要看闭环增量曲线的频率特性,特别是在高频时,下降曲线是什么样的,如果高频有凸起,则瞬态时,上升沿也会凸起,甚至震荡。

你认为相位裕度多少就算够了?

时域波形想要好看,60度是远远不够的,好好看看双极点运放闭环工作的理论。

电容充放电

拉扎维中文版教材P291有说明:“相位裕度的概念很适合于处理小信号电路的设计......大信号阶跃响应与......情况不符......”,下文也给出了电路有很好的相位裕度但很差的稳定性的例子。简单地说,交流分析的结果是基于电路的直流稳态工作点已经建立,零极点都是在此基础上确定的,但时域瞬态工作时,直流工作点的建立也是一个过程,稳态时的零极点还没有建立,因此导致了复杂的时间响应。相位裕度可能是电路稳态工作时能稳定的必要条件,但不是充分条件。

确如LS所述。瞬态跳变过程电路并不一定满足AC仿真所使用的小信号成立条件,所以造成了AC相位裕度不错但与瞬态结果却对不上。

相位裕度不够,一个30,一个50

把问题说清楚才能有目的的讨论。含含糊糊的说两句,大家也只有扯淡的分了。

phase margin調大的話(>60)應該就不會有shoot了

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:请教Sigma-Delta ADC中的带内谐波问题

下一篇:P衬底N阱工艺的nmos源级与体端短接,体端不接衬底,风险大吗?