电流源启动电路由问题吗?

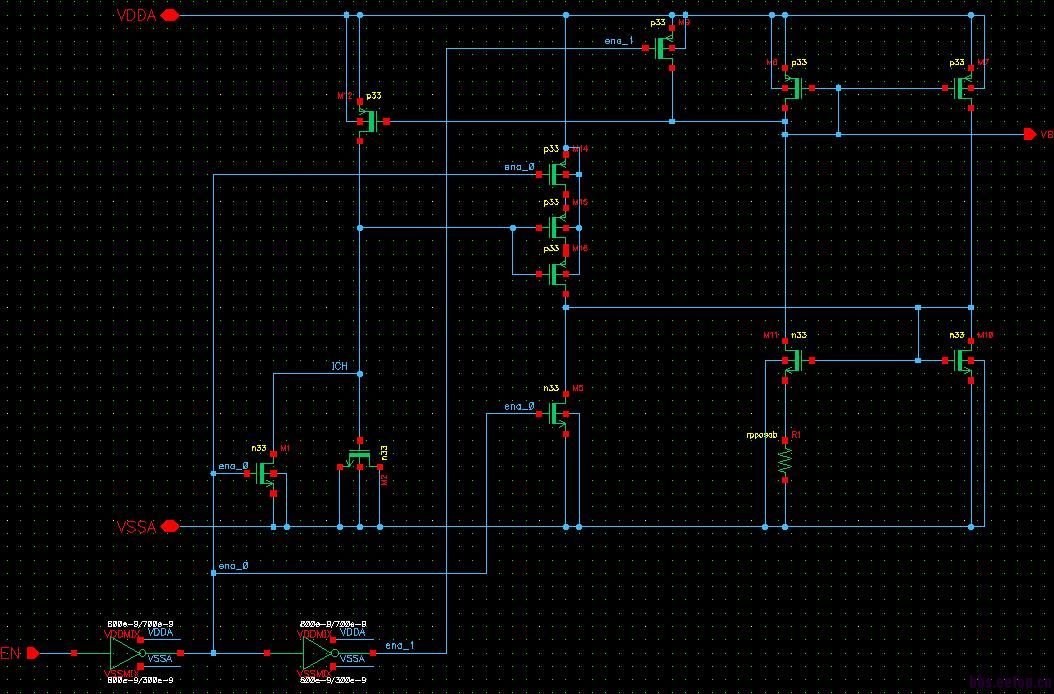

这个用电容当启动下拉,一直听说不太安全,说是在反复上电时有可能电容上面的电会放不掉,但是我仿真一直没发现问题;

这个用电容当启动下拉,一直听说不太安全,说是在反复上电时有可能电容上面的电会放不掉,但是我仿真一直没发现问题;

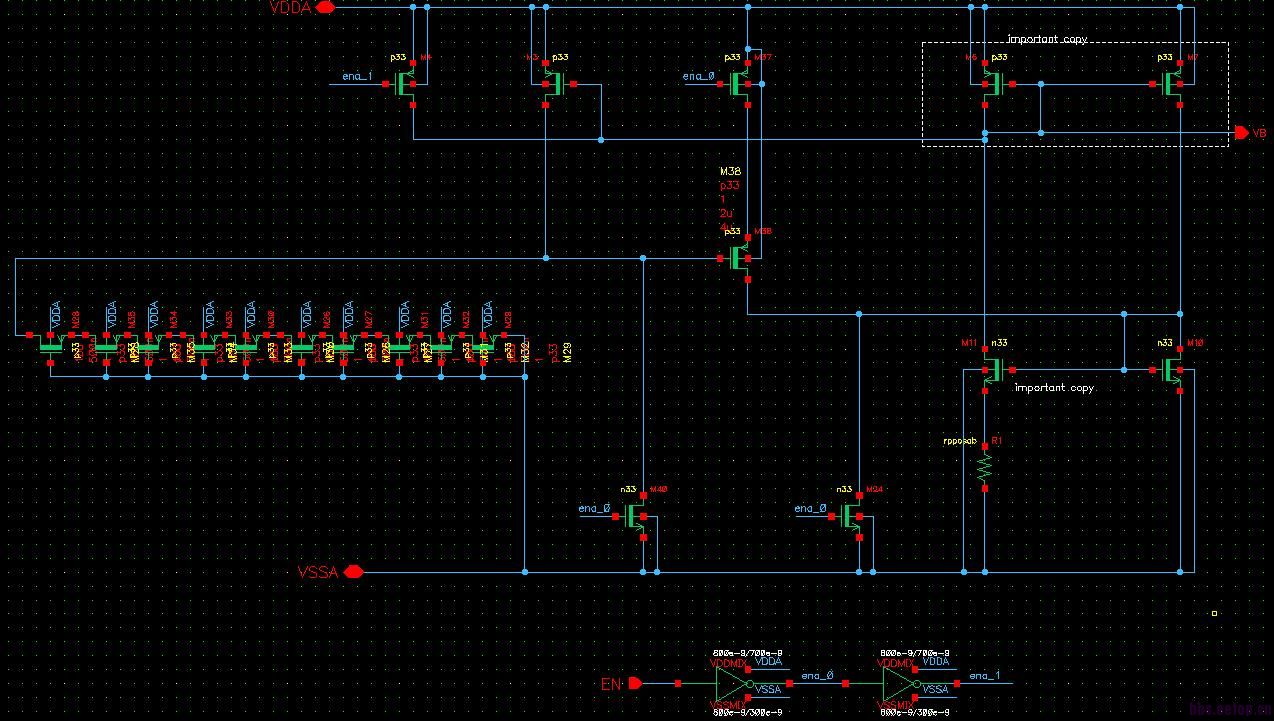

这个拿二极管连接的P管作为下拉管,有点当心没电流的时候有没有下拉作用,需不需要上面加个电流镜?

问下上图两个启动电路有无问题?有无BUG?

这个要看设置的静态电流的,和W/L有关,仿真看一下就知道了

启动电路不能引入太大的失调,或者说不匹配

就结构而言,第一个是有一定风险的,本人没用过,如果没有人用过并证明这个是可用的才敢用,其实不同应用下是不一样的,慢上电存在风险;

第二个没什么问题,我常用这种结构的启动。

补充一下,第一个结构sim简并点应该会存在两个简并点,第二个必定只有一个简并点,LZ可以试试看,如果只有一个简并点的话说明必定没有问题

简并点是什么?

越来越不太相信仿真

我也比较赞成第二种结构

具体的名词解释我就不说了,自己查资料,其实任何一个环路都需要做这样的考量,有多个简并点就意味着整个环路存在多个稳定的工作状态,就比方Bandgap有多个简并点的话,正常输出1.2V可以稳定,还有可能输出2V,或者0.5V的状态下稳定。一般正常能用的启动电路都能避免这个问题。

谢谢!

前面各位讲的都很有道理,第二种方案应用起来比较容易;但第一种也不是不能用,关键EN可以由power on reset电路控制即可,也就是V(ICH)变化从0v~vdd-abs(vthp)。

搞定了,谢谢各位!

我就用过第一种。但要注意控制上电延时能否时开启管导通。我第一次做了一批有出现上电快无法启动的现象。第二次改善了延时,测试没有出现问题。用这种结构是迫于工作条件,要在5v~40v内保证电流消耗稳定,不然也不会用这种结构。

谢谢,实践出真知,你说的比较有参考价值!再问下您,你提到的延时,是指EN在VDD上电后的延时时间吗?还是增大了上电电容或者是减小了启动注入电流?

第一种没有问题,只不过第一种的初始态一定要从电源上电后en=0的时候开始。

第二种可以用于en和电源同时加起。

不是,是mos电容下拉电位后,电位回升的时间,这个时间越长,m15m16越容易开启。

来学习的

两个启动都不是很好。第一种说白了就是不够肉棒斯特。比如EN先于VIN来;又或者EN有一个小的负pulse,N管电流镜gate拉低了,但电容上还没有,这时候再启动就锁死了。

第二种有quiescent current。

当然,不好不是绝对的不能用。

肉棒斯特。哥们您翻译的好棒。

门塞不缺,一看你就是个高手,高手这么多,我怎么混啊。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。