请教CT sigma-delta ADC 积分器差分输出共模电平不一致问题

录入:edatop.com 阅读:

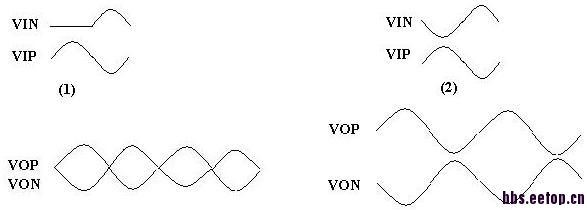

本人正在做一个CT sigma-delta ADC,仿真时发现积分器(RC结构)输出呈现上图这样子,导致整个系统无法收敛。不知怎么回事,请诸位不吝赐教。

你确定不收敛是共模的原因吗

回楼上的waner。系统不收敛,这肯定是一个原因了,如果一个信号总是大于另一个,下一级积分就不可能收敛了。我记得之前调单个积分器时,输出共模是一致的,但是后来再看,怎么都不一致了。不知是不是跟仿真条件有关,还是说没有DC 反馈通路,共模无法锁定?请做过的大神多加指导,谢谢!

今天又看,发现输入差分信号一个比另一个delay半个周期,输出正常;而直接用phase0和180设置输入差分信号,输出共模不一致。

没有共模反馈电路?无法稳定共模?

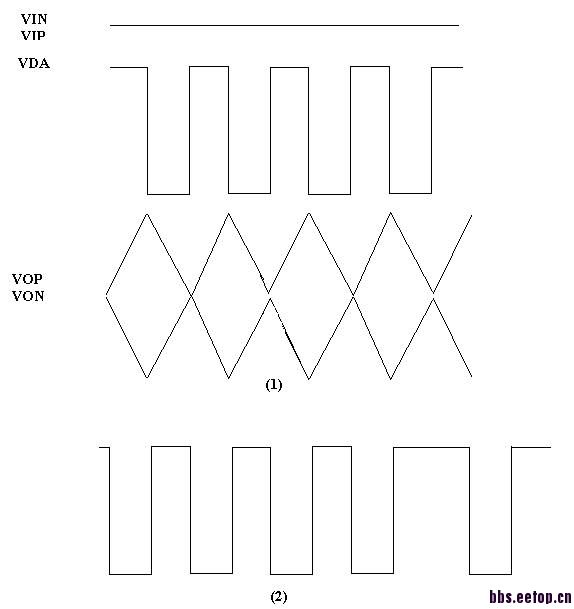

有共模反馈,带宽及稳定性都没问题。现在看来应不是积分器问题,直观看DC输入(共模电平)半个周期放电,半个周期放电,也没错。实际AD输出(正确的话)不是均匀pulse,而是如下图(2)。[attach]504330[/attach]

可以用METLAB 建模

之前先用Matlab建了模,看起来还是具体电路的控制没有调好。没有参考电路啊,全靠自己摸索:)

不收敛的问题找到了, 加和器第二个积分器输入接反了,matlab中的积分器不分极性,但实际电路OP输出分的。谢谢诸位关注本贴。

gfdgdfgfdgdgdfgfdgfd

diff amp is good for noise !

原来是这样啊

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。