请教:关于Gain Boost 结构

录入:edatop.com 阅读:

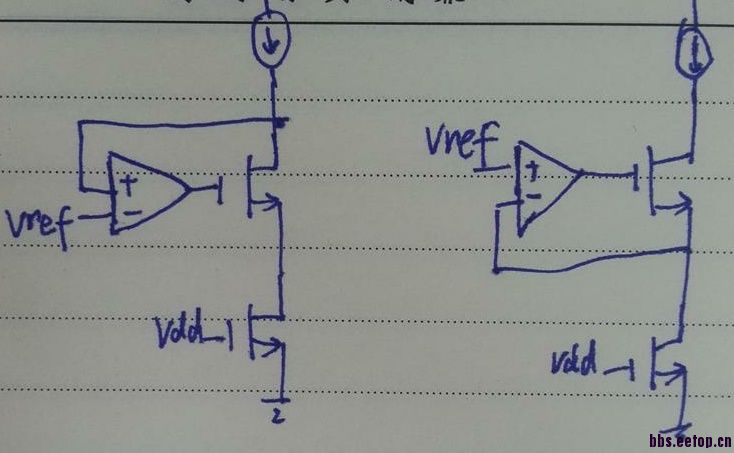

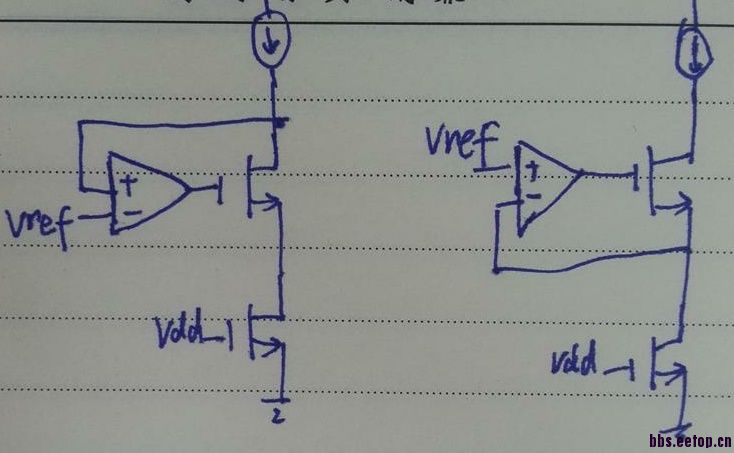

如图,常见的是右边的结构,放大器作用是增大输出电阻,但我的电路里面的结构是左边的图,小信号分析它减小输出电阻了A倍,怎么理解?

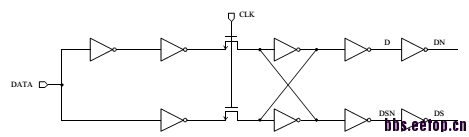

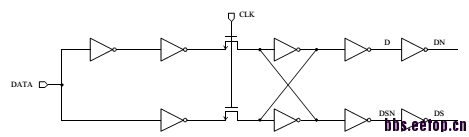

还有这个,信号是从左到右,怎么作为开关的nmos的源漏方向是那样子的,应该怎么理解?

还有这个,信号是从左到右,怎么作为开关的nmos的源漏方向是那样子的,应该怎么理解?

对于gain boost:

左边的电路,假如在输出点加一个交流信号Vt,那么由该电路产生的电流为A*gm*Vt,故输出阻抗为1/(A*gm),比diode连接的形式还小了A倍。

下边这个开关 drain 和source 接法随便啊...只要sub接最低电位就好了。source 与drain 哪边电位高 哪边就是drain

左边就是 2 stage opamp接成 unit gain

对没错,减小了A倍,我困惑的是为什么用这一结构,电流源不是要大的阻抗吗,现在反而小了A倍,难道之所以用这一结构还有其它解释?

我困惑的是为什么用这一结构,电流源不是要大的阻抗吗,现在反而小了A倍,难道之所以用这一结构还有其它解释?

如果用在cp中

replica会让内部voltage follow output voltage,输出阻抗是变小了,但是up和dn电流会match

你确定是电流源吗,最下面不是个开关管吗,输出阻抗小应该是电压源,输出提供电压等于vref的驱动。另外输出电阻应该除以loop gain,所以减小了A*gm*ro

正解!多谢!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:montacarlo分析不能输出30条以上的曲线?

下一篇:nanosimgui 出现segmentation fault