ADC中bootstrap采样电路问题

录入:edatop.com 阅读:

在进行SAR ADC的项目,目前进行到系统整体仿真阶段。遇到了瓶颈,搞了2周了都不知道问题在哪儿。前辈们,多多指教啊。

SAR ADC系统包括,bootstap采样电路,电容阵列(cap array),比较器(comp),寄存器和逻辑控制单元(SA Register)。

1、bootstrap采样后,进入cap array上极板,比较器立即比较。

2、通过SA Resigter来选择电容阵列中每一个电容下极板电压。

问题描述:

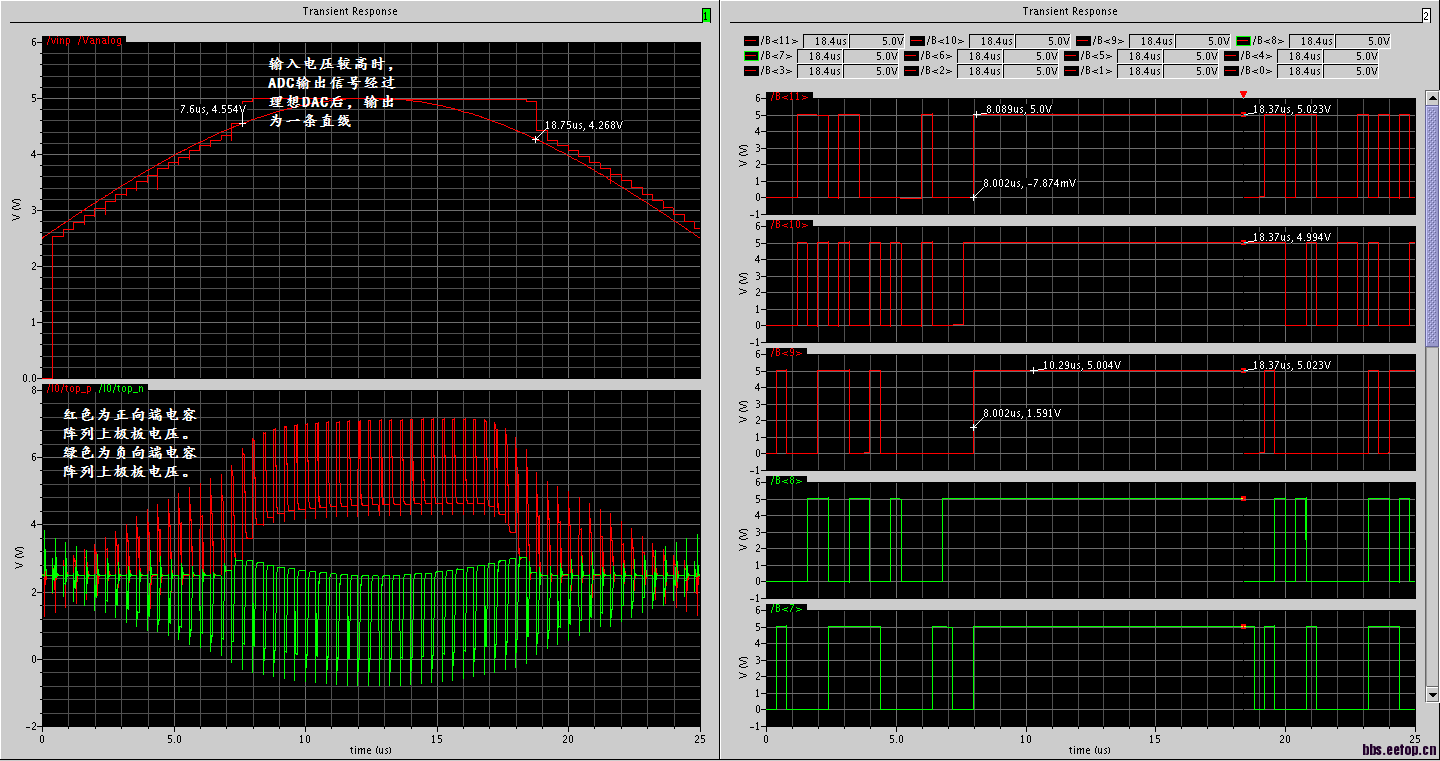

输入信号高为共模值2.5V,振幅2.5V,频率20k的正弦信号;采样时钟5M。

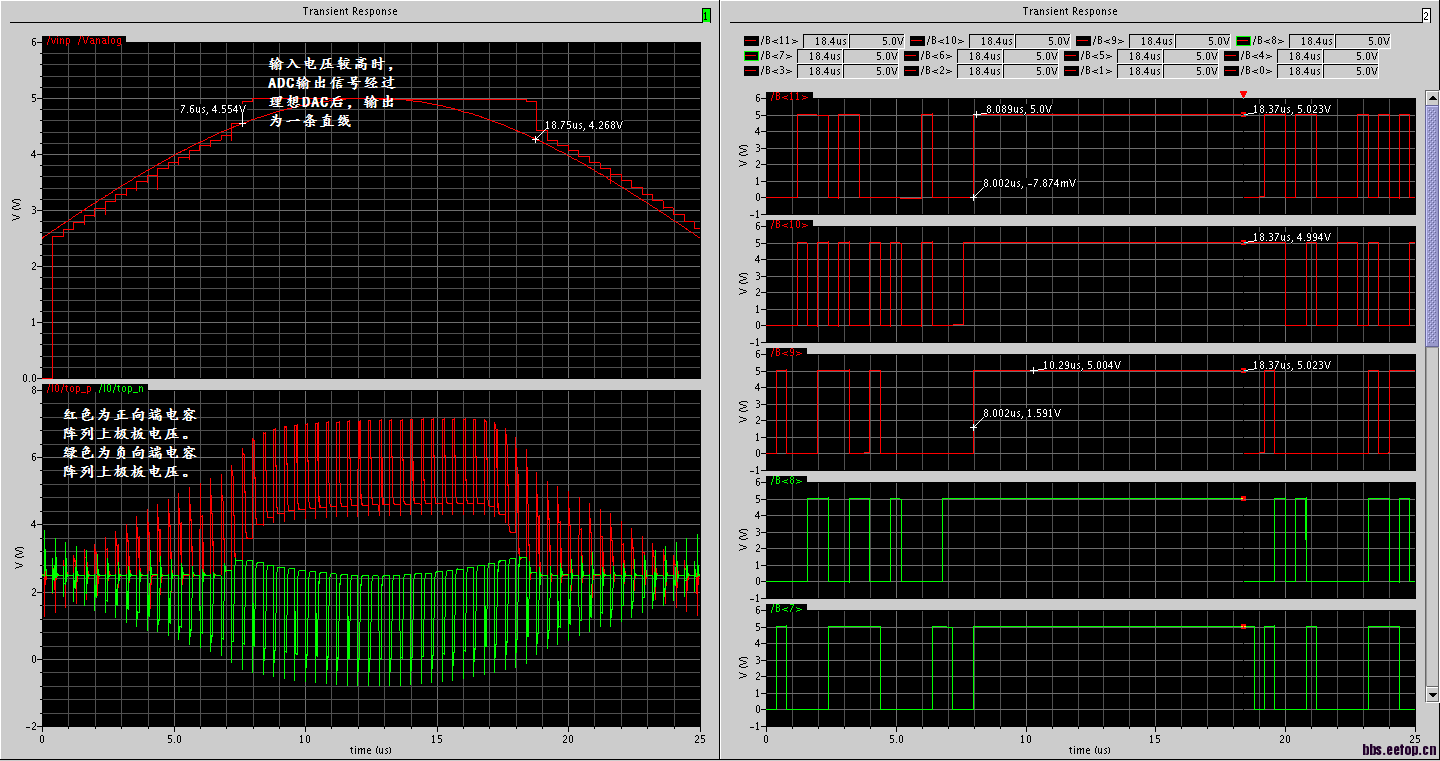

当输入信号的幅度高于4.5V时,ADC输出严重错误,表现为恒为高,通过理想DAC后位一条高电平直线。而当幅度小时,则无此现象。

截图如下:

检查每一个模块后,发现bootstrap采样电路当输入电压较高时,就已经出现了采样不准的情况,考虑是否由于采样失准的原因造成输出错误。

可是,减小输入信号振幅后,输出信号依然在高位出现上述错误。

不解啊,前辈们帮帮忙吧。

SAR ADC系统包括,bootstap采样电路,电容阵列(cap array),比较器(comp),寄存器和逻辑控制单元(SA Register)。

1、bootstrap采样后,进入cap array上极板,比较器立即比较。

2、通过SA Resigter来选择电容阵列中每一个电容下极板电压。

问题描述:

输入信号高为共模值2.5V,振幅2.5V,频率20k的正弦信号;采样时钟5M。

当输入信号的幅度高于4.5V时,ADC输出严重错误,表现为恒为高,通过理想DAC后位一条高电平直线。而当幅度小时,则无此现象。

截图如下:

检查每一个模块后,发现bootstrap采样电路当输入电压较高时,就已经出现了采样不准的情况,考虑是否由于采样失准的原因造成输出错误。

可是,减小输入信号振幅后,输出信号依然在高位出现上述错误。

不解啊,前辈们帮帮忙吧。

站内信告诉我你qq,我最近也在搭sar,一起交流下。

bootstrap bootstrap

check mos substrate !

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。