sar adc中DAC(电容阵列)模块,疑问!

录入:edatop.com 阅读:

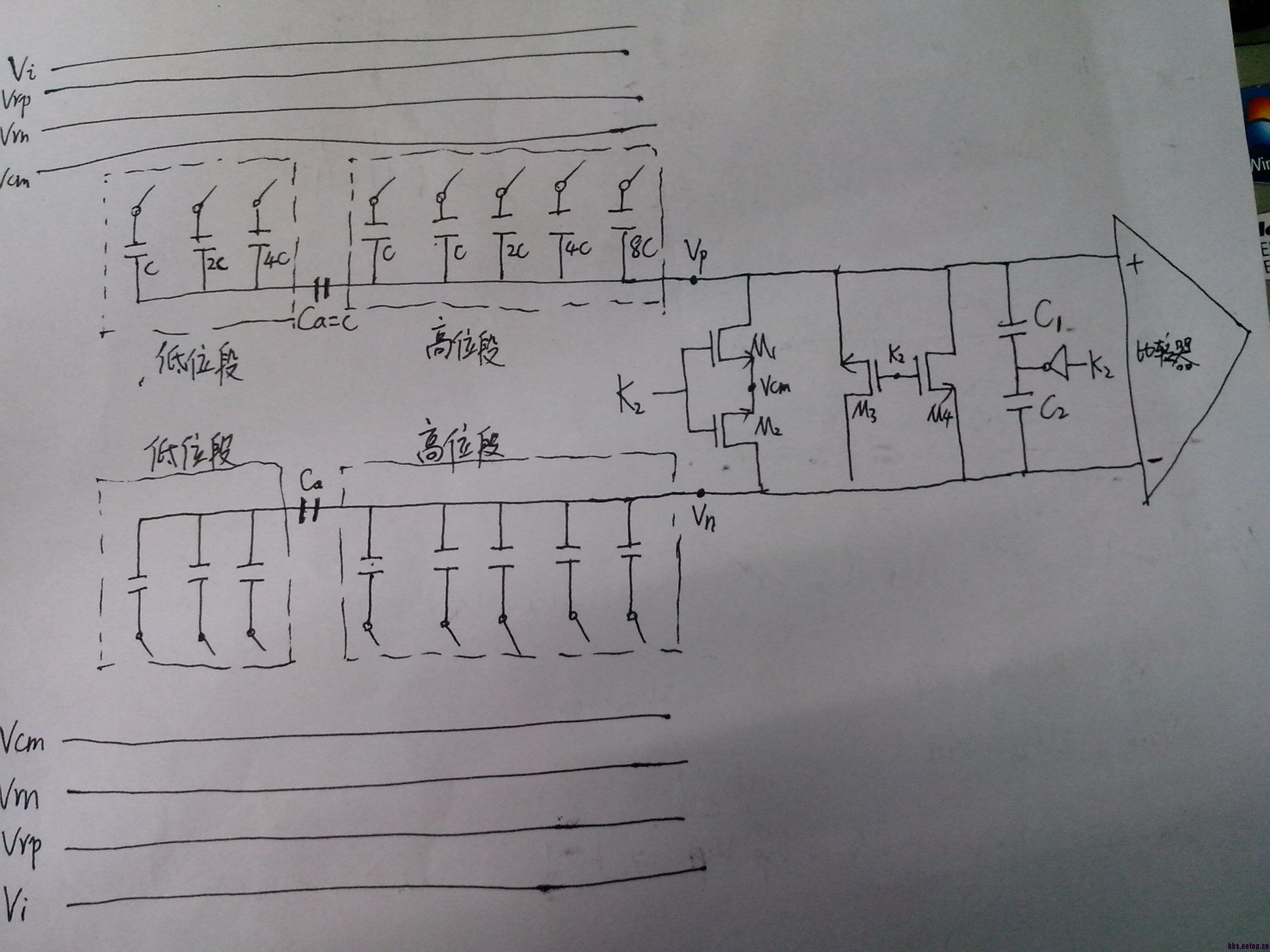

最近在做sar adc,差分输入, 输入采样仅仅是高位段参与,低位段不参与输入采样。 DAC部分不应该需要开关部分和电容阵列部分吗?下图的电路中,M1、M2负责实现输入采样时的开关,M3、M4以及C1、C2是起什么作用呢?其中:Vrp=4V,Vrn=1V,Vcm=2.5V,Vi是处于1V~4V的正弦波。

求大神们指教!

每个电容的底板当然不止一个开关,高位段的电容底板接三个开关,分别连到vi、vrn、rvp;低位段的接两个开关,分别接vrp、vrn

m3、m4也是采样开关的一部分,而且是核心部分,m1、m2更多的是gei电容顶板充电至vcm用

c1、c2大约是用于调节conversion phase电容顶板共模电压

有了M1和M2不就已经可以保证对输入采样了么?M3和M4的作用就相当于将vp和vn连接至一个电位的作用么,怎么M3和M4是核心模块呢? 这些知识您是从哪儿知道的?有什么参考资料吗?

M1和M2在断开时会有电荷注入到节点Vp、Vn上,它们的电荷注入会存在一定失配,M3、4就是用于消除这个失配。参见razavi第十二章。

论坛里资料多的很,看你愿意花多少时间精力去研究了。

恩,好的,谢谢!

请教,为什么一般这种电容列阵结构的 LSB列阵(低几位)不参与采样呢?

我认为将LSB列阵下极板也加3个开关,参与到采样中,可以消除满量程误差,也没用带来什么问题呀。

good description !

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:一种比较器输入端与信号输入端直接相连的SAR ADC,大家见过吗?

下一篇:求单斜ADC的INL和DNL的仿真方法