一种比较器输入端与信号输入端直接相连的SAR ADC,大家见过吗?

录入:edatop.com 阅读:

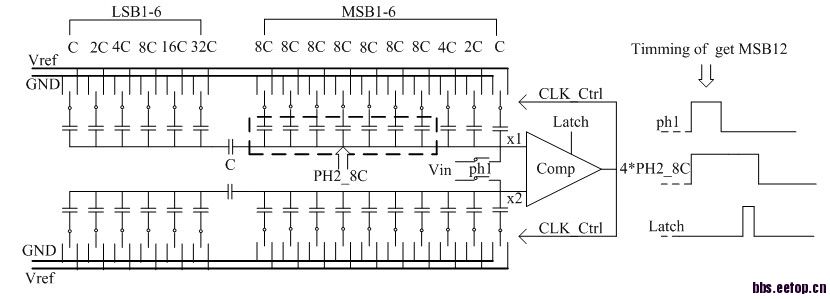

请教各位,有哪位学过SAR ADC的大牛见识过电容阵列这么排布、输入信号这么采样的?

输入信号采样时直接接上比较器的输入端,由高位到低位的比较直接依次选择相应的电容端,公式推导的结果是这种结构的SAR ADC比较器的输入端处的寄生电容将会引入相当大的误差。但是现在也不知道其与经典结构相比的好处在哪里,为什么牺牲这么大的误差,为了得到什么?

输入信号采样时直接接上比较器的输入端,由高位到低位的比较直接依次选择相应的电容端,公式推导的结果是这种结构的SAR ADC比较器的输入端处的寄生电容将会引入相当大的误差。但是现在也不知道其与经典结构相比的好处在哪里,为什么牺牲这么大的误差,为了得到什么?

2012-7-13 15:36

这种方式采样方式好像叫上极板采样!这种采样方式使电容阵列减少了2^N/2,而且较小了电容再分配时的功耗

2楼正确

上极板采样技术 (区别于常见的下极板采样 ),采样开关必须采用VGS恒定的boost结构。

比较器输入端得寄生电容仅仅影响DAC的 增益误差(是DAC而不是ADC),不影响ADC线性度。

上极板采样技术结合恰当的CDAC switching 方式,可以降低功耗,简化SAR ADC logic设计,提高速度。

当然,还有二楼说的 电容减半(很多结构可以电容减半 )

good architecture !

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:ADC的精度与运放的增益

下一篇:sar adc中DAC(电容阵列)模块,疑问!