请问PIPELINE ADC中运放输出电压的过冲问题

录入:edatop.com 阅读:

结构是shaless,目前时钟周期为3.2n,仿真表明,采样结束后直到比较器输出花掉了0.5n,这样剩下了1ns给运放,出现的问题是:由于N个比较器的比较速度有差别,所以有的结果先出现,有的晚一点出现,导致运放有很大的几率先向错误的方向建立,而后再掉头回来,导致建立时间大大延长,有没有好的方法可以解决?

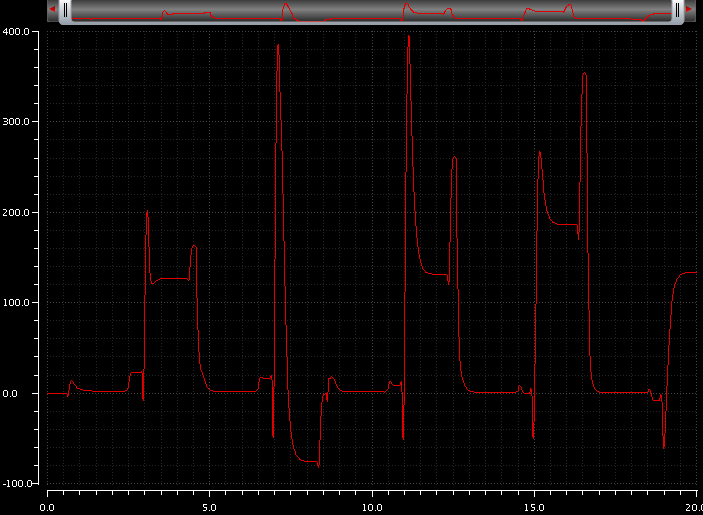

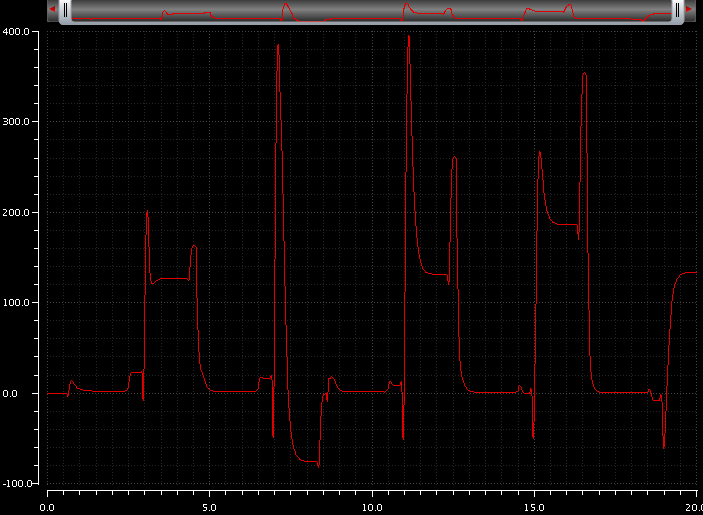

运放的输出见图,比如第二个值

运放的输出见图,比如第二个值

没有什么特别好的方法,我能想到只能是设计一个更快的比较器,在信号到达比较阈值附近时比较器输出能够尽快的脱离无效区域,另外就是用保把保持相的时钟做一下延迟,在所有比较器的结果正确后,再去锁定本次的结果。

恩,谢谢,这个问题确实无解,只能让所有模块都快点 再快点

swtiching spike?

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。