环路仿真出现右半平面的极点

录入:edatop.com 阅读:

我在使用大电感和大电容仿真带隙基准的环路时,发现不同的断点加信号得到的仿真结果不一致,有的断点更是出现了右半平面的极点,请问这是为什么呢?

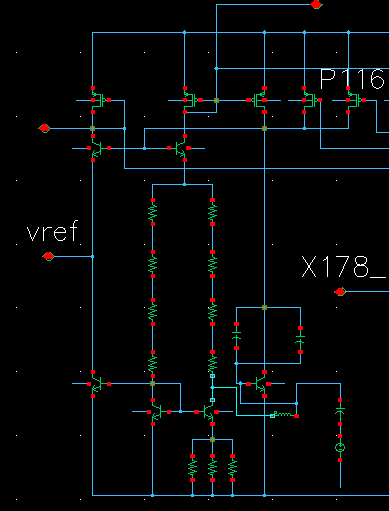

电路图: 仿真的断点也在上面了,电感1G,电容1G,

有多个环吧

确实有多个环,那这个右半平面的极点是由于多个环的共同作用引起的还是由于那个大电容大电感的仿真方法引起的?

最好贴图吧

传统的带隙基准的话应该有两个环,一个正反馈一个负反馈

我后来又仿了一下,去掉一个环就没有那个问题了……

电路图: 仿真的断点也在上面了,电感1G,电容1G,

仿真稳定性用stb仿真,另外,拆环的点很重要,对于采用运放的典型的Bandgap来说,存在正反馈,负反馈两个环路,拆环点应当选择运放的输出那一点

经过我在不断的拆环点的尝试,发现确实是在运放的输出点断环比较合适,我在运放的输入点断环就出现了右半平面的极点,但是这怎么解释呢?stb仿真简单的了解一下,好像些许麻烦…

你单看正反馈的环路,自然就有RHP的极点了

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:运放失真、输入输出波形

下一篇:求助AMS数模混合仿真