请大神分析下这个上电复位的原理

录入:edatop.com 阅读:

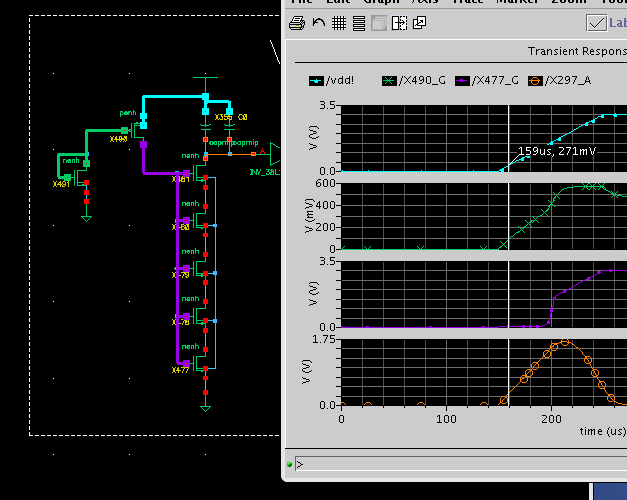

电源是模拟一个上电过程的脉冲信号了,但是各个信号的原理不是很懂,如图中我用了一条竖直的标记线,在标记线与绿色信号线相交的那个点的地方不是应该是低电平吗,那对应的电路绿线所在的p管不是应该管子开启了从而使紫色信号线拉高电位吗?但实际P管还是关闭的,为什么啊?大神,救救我这个苦命的娃吧

要考虑电源电压是从0到3.3V的,紫线拉高是在Vdd>vthn+vthp之后。

标记线处的绿线之所以会高,是因为P管Cgs的存在,Vdd上升,P管gate也被拉高。

这个电路类似于power ic里bootstrap cap的做法,电容两端电压不能突变(就像电感流过电流不能突变一样)。Vdd上电,Buffer输入端也被拉高(电容两端电压不能突变)。

此时P管有Vgs电压,导通。拉高接地的串联NMOS群的Gate,NMOS们导通,慢慢泄放Buffer输入端电压。

你算一下Vgs,不就知道p管有没有开启啦

Then the AC coupling cap has to be large?

Cap 大小跑跑仿真啊,太大可能用 外接 AC Cap?

这个POR在实际成熟产品中用过么?

该电路抗干扰能力不行吧,打ESD容易复位

谢谢大神,小弟初学不久,这个电路自己仿真分析了之类也明白了,谢谢,正因为有你们的提示和教导,我才能不断进步

大神谢谢

内容这个电路只是原理,4楼讲的很清楚了,但是不能使用,时间常熟大,跳变沿不够陡,应加入正反馈!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。