欢迎大家留言、帮顶---ADC测试求助帖~

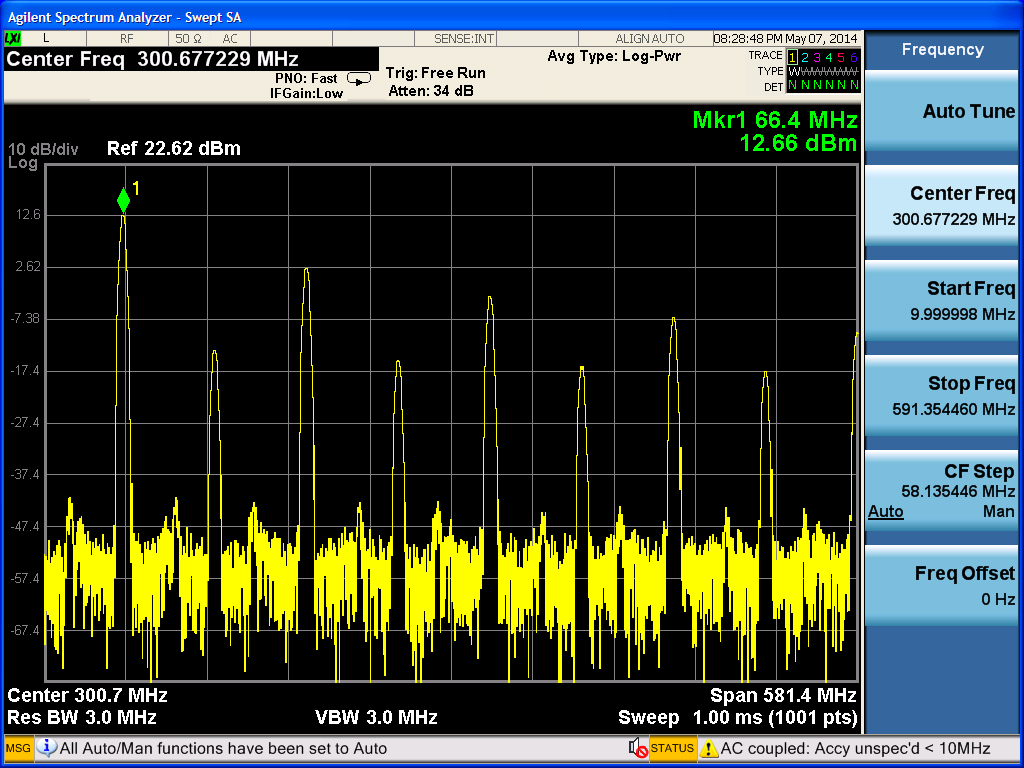

由于没有高稳定低相噪的时钟源,采样时钟是用FPGA产生的,其频谱如下:

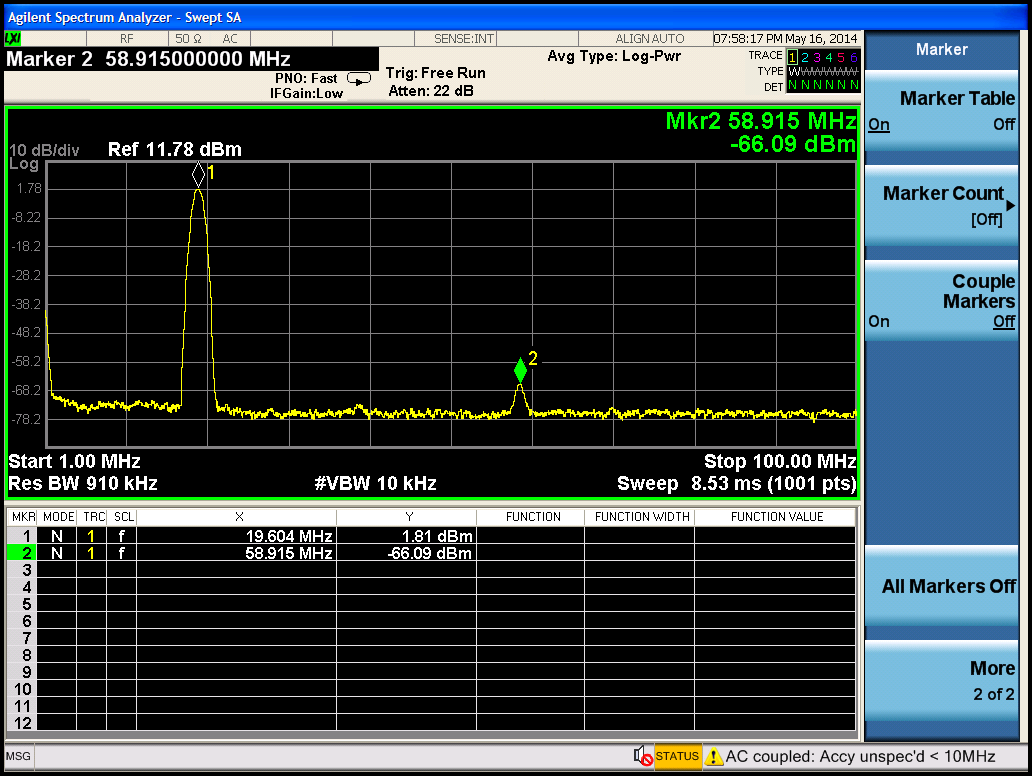

模拟输入进入单端转差分电路前加了个低通滤波器(自己做的个简易LC Filter),信号如下:

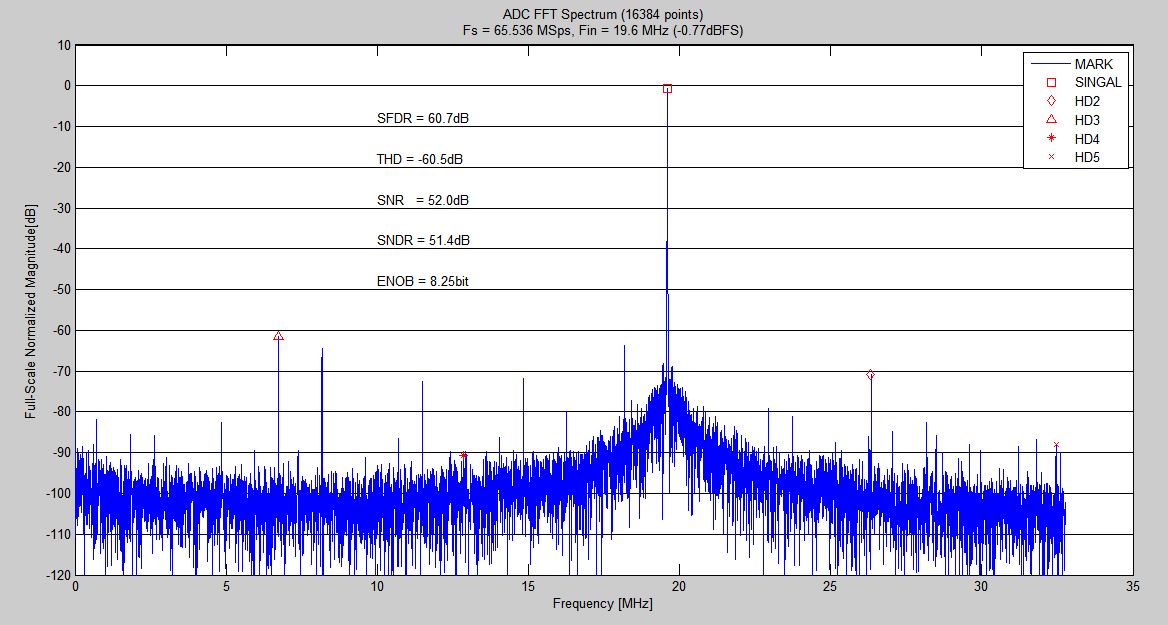

测得的结果如下:

相比加滤波器前,SFDR有10几dB的改进,SNR及SNDR都有改善。但目前还是离理想的结果很远~

请问大家:

1、我的输入信号达到了去评估该ADC(12bit、65MSPS )的要求没有。没有差分探头,我也没去看变压器(差分运放)输出波形

2、时钟谐波好多,它对动态性能评估有多大影响,我想把SFDR测到80,ENOB测到11bit,这个时钟信号不能达到要求吧

希望大家基于以上情况给点建议~谢谢上次fuyibin 和lonerinuestc两位大神的建议,再次感谢他俩!

帮顶!

时钟是方波,有谐波很正常。

你可以把你的时钟信号进行一下jitter评估,根据snr=-20*log(2*pi*fsig*t_jitter)来粗略的预估一下。

但是datasheet上给的时钟输入要求是:低相噪正弦波!(注:PCB板上有时钟整形电路)

多少频率的时钟?100M以上的话,你用fpga产生时钟,ENOB可能会掉2bit以上,采样频率越高,影响越大

65M

我感觉有如下问题:

1. 输入信号的近端相噪声过大,所以你的SNR很糟糕,并且从你的频谱仪结果来看信号3次谐波很高,所以滤波器有待改进。

2. 时钟的话看频谱没有意义,跟谐波没关系,你得测他的相噪曲线,尤其关注远端相噪。如果你觉得时钟jitter比较差,先灌个低频输入试试

很是赞同!谢谢~

时钟也要滤波,最好买个PLL来产生,如果条件有的话

建议你到agilent的开放实验室去测试,用他们的E8663D或者8257D带低相噪模式的信号源测,再弄一个好点的BPF,立马解决问题

65M clock就是FPGA里面的PLL宏模块生成的,你指的是直接买个“硬件上的PLL”么?

唉,才知道Agilent有个开放实验室~就目前情况,估计还是得自己去摸索。现在最想搞一个好点的时钟源,淘宝上定制VCXO可靠么,或者别的途径?

别费劲了,好的OCXO很贵的,并且买不到,直接去Agilent那边凑合测测得了

FPGA上的时钟不是很好啊,给数字电路和给高精度ADC的要求当然不一样啦,我一般是先用信号发生器产生一个时钟,通过一个无源滤波器,然后通过一个 PLL的芯片,ADI和TI的都行,你可以取选一个合适的

你的无源滤波器是在哪搞的啊?用ADS仿真,再用LC焊一个可以么

买的,资金多,随便买,呵呵,无源滤波器还挺贵的,一个100多呢

求购买渠道或者链接

lone侠,我现在用e8267d测试一个14bit 20M adc,时钟用的e8267d的前面板rf输出,输入信号用的e8267d背部iq差分信号直接灌,未加filter,但e8267d的iq设置里有个40M低通模式,开启后sndr到62,开启前到59,此外还试过用iq信号的其中一根接低通滤波再接balun给adc,效果很差,sndr才50不到,因为手上只有一个滤波,无法给两根差分信号同时滤,请问这种情况该怎么改进?

另外,e8267d适合测12bit级以上ADC吗?谢谢

我所知道的的最好的信号源肯定是R&S SMA100A,但是8267D已经非常好了,用来测16位都没有问题,当然需要选配low phase noise选项。背板IQ没用过,我们平常测试是用两台信号源(测two-tone用3台)。你试试用前面RF输出作信号,后板做时钟呢

两台信号源倒没问题,那测试的连接方法是什么呢?是不是时钟和输入信号分别从两台信号源的前面板rfout出,输入信号经过filter和balun到板子上,这样对吗?我这里的balun是minicircuits的ZMSCJ-2-1,filter是minicircuits的VLFX-80,请帮我看看这些器材是否合适?谢谢lone了

连接方法肯定是这样的。至于balun的话,你得注意下他的频带是否合适,还有就是比例(1:1或者1:2)以便正确的阻抗匹配

求交流啊,你的QQ号多少

原来FPGA门驱动电路抖动有十几甚至几十ps,用它做采样严重影响SNR

现在进展怎么样了,有机会交流下啊~

是的,即使我们测试低速的SARADC,时钟也不会用FPGA来提供,时钟的驱动能力也是需要考虑的,不过这个从示波器上就能看出来。

苦逼啊,示波器带宽不够,看到的都是正弦波!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。