仿真值和流片值的差异会有多少

没有提取寄生的参数进行后仿真,那么最终流片出来的这个PMOS功率管的导通电阻会变大多少?一般是个什么倍数级别的?(不考虑封装,只考虑晶圆)

再顶一下,求高人指导啊。

放心,应该是一样的

我觉得你应该转换一下思路,你想知道Rdson应该是为了知道这个管子消耗的功率从而计算发热量吧?如果是这样的话你不妨关注电流通路上其他地方更大的电阻所造成的发热,关注主要的点。

或者直接用红外测管芯温度。

Rdson=33mohm 是LDO还是DCDC?

导通电阻 还是从负载上去考虑比较好

就是这个通路上面的电流最大。PMOS管一端接电源,另一端接电阻,电阻在芯片外面。

其实我就是想知道仿真值和流片值的区别到底有多大?

因为现在老有人在耳朵边唧唧哇哇的说PMOS管的导通电阻最多只能做到120mohm,面积再大也不行,不晓得这个值是怎么出来的。

没有电感的BUCK+LDO,电流通路就是一个PMOS管+一个电阻负载。

不用考虑MOS管自身的走线电阻么?用了三层metal。

关于最小导通电阻是多少这个是从器件级的研究来的。搞这种研究的设备就非常复杂,不是一般公司handle的了的。我的意思是你的电流通路中,可能via之类的接触形成的电阻就已经大于33mohm了。所以管子不是主要的。

恩,的确是这么回事。那麽样优化走线以及接触孔的,来降低电阻值呢?或者说有什么方法可以仿真出来或者评估出来的?

方法无非就是多打孔,加粗线,甚至2~3层走线。接触孔和线阻的数据在工pcm艺文件里都可以找到。max 和 min的数据一般都是靠谱的,用这个数值大致估算下就行了。做工程没必要再这个细节方面抠那么死。那是中科院干的事情。

恩,明白了。那根据你的经验来说,CMOS 5V工艺的PMOS管的导通电阻最小可以做到多少?

小编说的应该是没有电感的boost加LDO吧

没考虑过这个问题,sorry。

小编还在为这个问题纠结吗?这个跟工艺和版图关系比较大,特别是金属的厚度,要做到120毫欧以下其实很容易,这还是算上打线电阻的情况;我们有产品做到60毫欧左右。

在大电流下, 你仿真和实际差距是比较大的, 寄生参数影响非常大,而你仿真没有考虑的

恩。我是在想有没有什么比较可行的仿真来验证这个问题呢?还是只能靠估算或者测试?

恩,你这样说的话,我心里就有底了,至少是可以做出来的。

最讨厌别人说这个做不出来,那个不能做,自己又不去找原因,还不让别人去尝试。

金属线厚度增加,相当于增加截面积,所以线电阻就会小一些。

那你能不能说一下你用的多大的工艺,金属厚度是多少,可以给我参考一下。

先谢谢了。

你这么说来是整条回路上的总电阻了。话说是用顶层厚铝工艺的么?

不知道你版图处理的怎么样,保守估计应该在60毫欧,如果版图处理不好的话100以上也是正常的。主要的电阻就是寄生的那些。

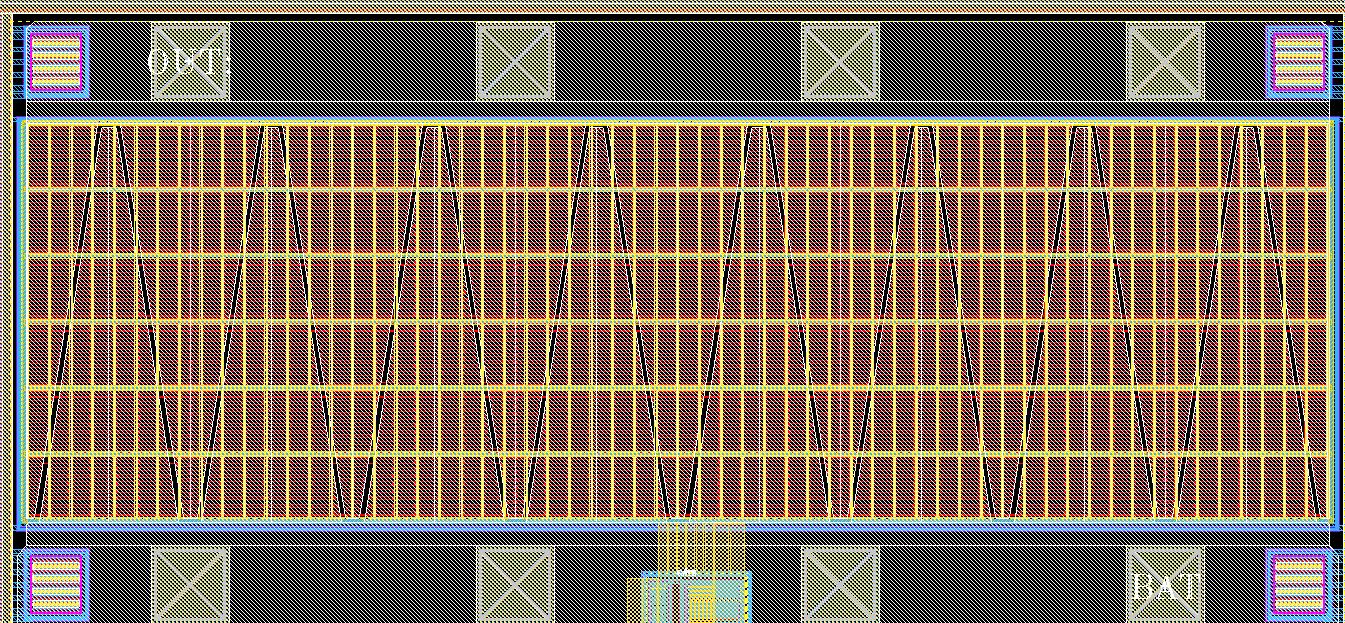

版图画法见图片。顶层用的是加厚的铝线,不知道这样布线是否合理?

经过测试确认了一下,流片值比仿真值大了20mohm的。常温下,加上ponding wire,差不多92m的样子。

测试导通电阻过大,主要是芯片散热不行,温升太猛烈了(输出2A电流的时候)。

谢谢各位的热心指导!

虽然和你期望的相差有点大,但在我看来依然是个不错的结果。

温升严重可以试着把调整管单独拉到一个空旷的区域,把管子铺的开一些,再把金属尽可能的铺大。

看起来这个烧了不少面积在散热上有点浪费,但是发热厉害影响到周边管子最终还是会压下你的yield,所以还是有必要的。

what type of package do u use?COB?

不太会吧,那个还要设计板子,而且自己打线真是个累活。

MSOP8,不带散热片的

哦,你评估测试时也采用这种封装而不是COB封装?

恩,是的,没有做COB封装测试。

恩,后续的确该这么做的。

设计不好,误差很大(如50%)也是很可能的。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。