cmos功放设计出现漏端电压差分性很差

录入:edatop.com 阅读:

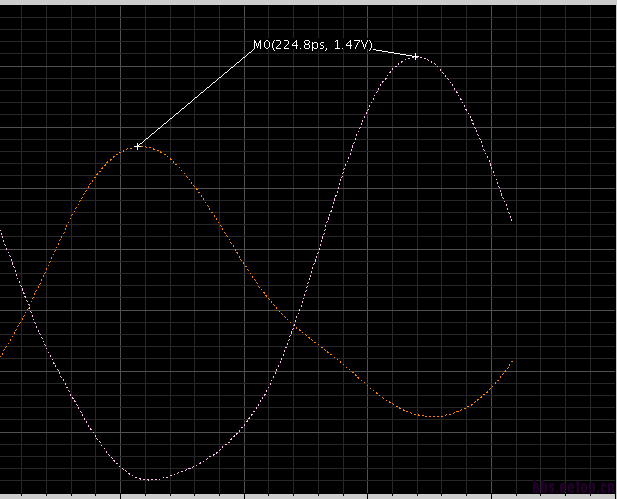

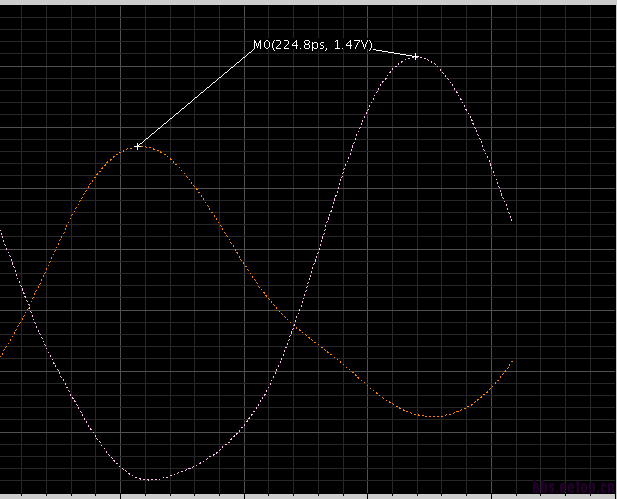

我输出级单级仿真的时候发现漏端电压差分性还行,但是两级联防的时候出现问题,我仿pss,输出P1db=25dbm,但是差分漏端电压峰值差了很多,电流差的不是很大,因为输出阻抗匹配我是用信号匹配方法设计的,可能是在大信号情况下差分阻抗不是平均分配造成的,希望大家能讨论下。这是差分漏端电压的波形:

,,

,,

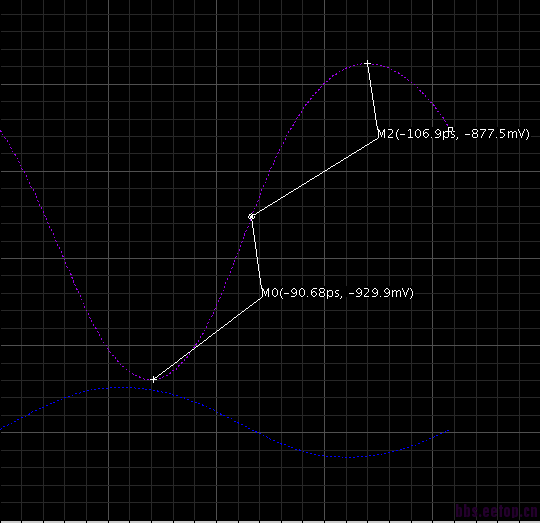

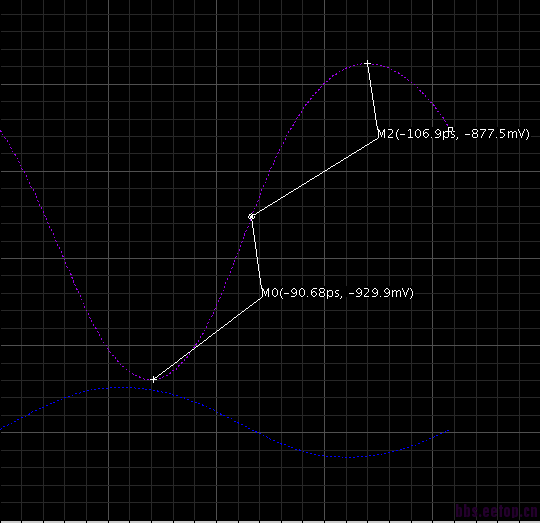

还有一个问题就是,我看了下不管是第一级输出波形还是第二级输出波形,都是正半波形和负半波形的时间长度不同,也就是类似占空比不是50%的正弦波,我看了下,是输入栅端的电压高于vbias时输出漏端的波形时间长度小一点,会不会是高于Vbias时电流大,充电时间短造成的。图是下面这个

,,

,,还有一个问题就是,我看了下不管是第一级输出波形还是第二级输出波形,都是正半波形和负半波形的时间长度不同,也就是类似占空比不是50%的正弦波,我看了下,是输入栅端的电压高于vbias时输出漏端的波形时间长度小一点,会不会是高于Vbias时电流大,充电时间短造成的。图是下面这个

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:Chopper modulation 和 放大器增益

下一篇:寻爱好TP的道友