轨至轨运放

刚才好像发错地方了= =....小编帮忙吧资料区那个帖子删了吧......囧..

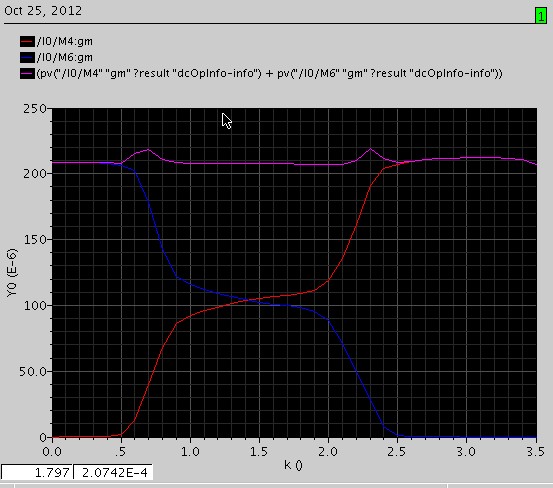

最近在在做一个轨至轨运放,用的是齐纳二极管的结构,但是遇到了两个问题,第一个是恒定跨导曲线中间变化部分不是两个凹点而是两个凸点......与文献刚好相反.....

第二个就是class-AB输出在高的共模电平下相位裕度要比地共模电平下小的多(大概小8-9°),我问了一下师兄,有的说是因为P管尺寸较大(N管5倍,由迁移率以及实际工作测试确定的)的Cgs寄生电容比较大的缘故。是这样的吗?有什么好的解决办法吗?

求大神帮忙解答

一下啊

没图怎么说啊

图片传不上来.....,高电压是有相位裕度有65°左右,而低电压下却有接近75°

还有,这个相位裕度是通过调大了输出管的宽宽长比才的到的,现在流过输出管的静态电流大约有120u了......好大....如果减小的化相位裕度又不够了= = ....这个要怎么办......

图片上传老是失败......

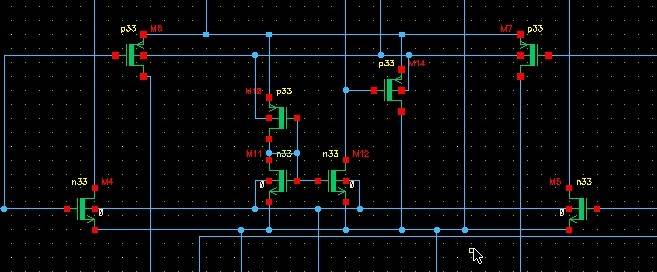

有图了.......

这个都是正常的。输出电平上升时下面NMOS的RDS增加,上面PMOS的RDS减小,当在中间某个电平时相位裕度最小,DC增益最大。

如果随着共模电平从VSS-VDD变化,相位裕度先减小再增加,最后图形成一个凹形,这个我知道是正常的....问题是仿出来基本是随着共模电平的增加,相位裕度呈递减的趋势..... 0v的时候有70多度,到VDD=3V的时候只有65左右了,这还是将输出电流增加得很大的结果,如果输出电流维持个80u左右的一般值,那3V时候的相位裕度只有56左右.....

那你分析下为什么是正常的,两个电阻并联的值又小的那个确定,说明你的NMOS的电阻一直是小的,出现相等时不是在中间电平。当然接近电源电压是就当别论了。

电源电压是3V 出现相等是在1。7V左右 这个应该正常吧

很正常。一般比0.5VDD大点。

这会回寝室了,明天再看看...如果要减小输出的静态电流,有什么办法能保持相位裕度不变吗?

我觉得增益还是正常的

gm 现在的变化率在4.8%左右,数值和效果是正常的,就是不知道这个曲线的凸点是不是正常.......

还是米勒补偿,可以看看模拟集成电路设计精粹,sensan的。

不是补偿不够的问题,我算过的,补偿电容是够的。我按着减少寄生电容的思路去改了一下,减少了面积,发觉效果好了一些,不过现在我已经用到最小尺寸了.......

还是谢谢解答哈

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。