DAC输出接近VDD时阶梯恶化如何解决?

确定运放工作在rail-rail范围内,增益变化多少?5V,8bit的DAC最大输出应该是4.98V左右,看看switch的P管size够不够,采样settling时间够不够

我输出8个零的时候是19几毫伏,所以说输出8个1时应该输出5v.现在是很难达到5v,而且也不太可能,目前只能达到4.985.我想还可以提高,但是现在找不出办法.你指出的settling时间是否足够确实是应该注意的问题。我换了下时钟,发现输出阶梯好多了。switch的管子会尺寸很大,不晓得除了加大管子尺寸还有什么好的方法

全0的时候输出18mv,说明有offset,为啥不想着消除offset而要去做最大电压到5V?,确定你的运放在rail-rail情况下工作完好?增益和带宽满足要求?看看有没有gain error? 要是有gain error的话,也不能做到rail - rail。 switch size, load cap,resistor value and clock frequency,自己折中吧

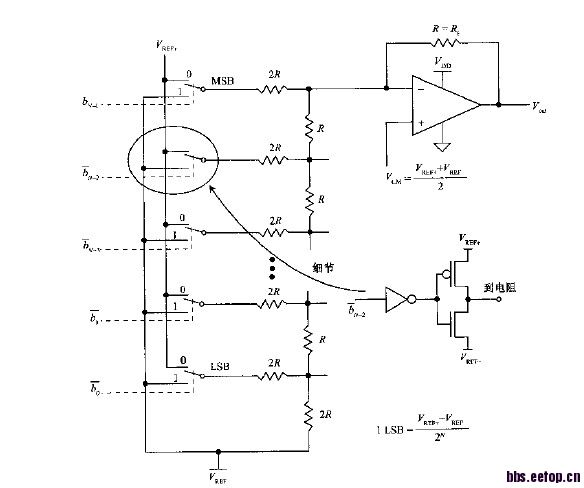

全0的时候输出19多mv不是因为offset,而是我的结构决定的。Vout=Vref*(1-(1/2*b1+1/4*b2+...))。所以消除offset实际上就是让最大输出接近5v。不知道前辈如何评价这个结构对运放的要求。感觉还不太会分析。

问一下,这个dac不要op,直接输出可以吗

5V电源,输出信号0-5V,这spec谁定义的?纯粹胡扯蛋,拿根金属线直接连到输出还有一定的电阻呢,带不了电阻负载

正解!

我知道电流型的是肯定不能输出完全的5v。所以我只是想尽量接近,至少能在0.5个LSB的误差内,也就是离5v还差0.5个LSB。而且看了些芯片资料的介绍,通常都说他们的dac有rail to rail 的输出,请问如何理解?

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。