LDO中第一级运放类型的选用问题?

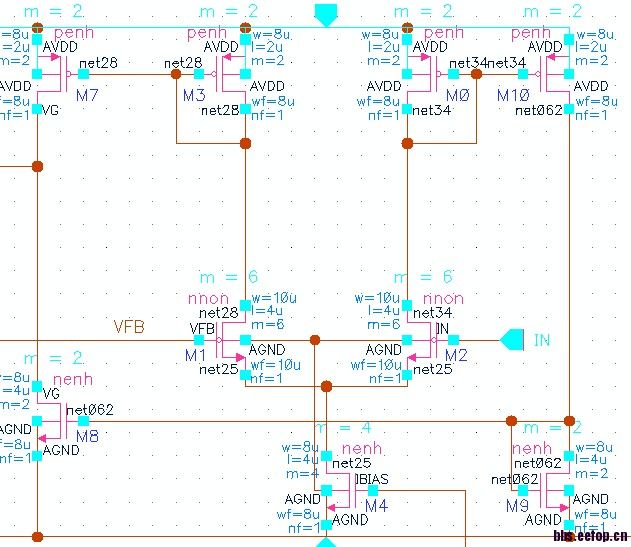

图1

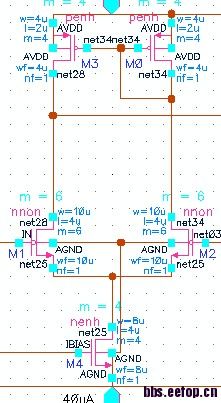

图2

full swing,更对称

采用OTA

第一个是对称ota,不过负载电流镜取1:1蛋疼啊。取个1:3或者1:4好些。

如果是低功耗设计,1:1也很正常

低功耗,为什么要用这种高功耗高噪音单极运放结构?(相对于普通的单极电流镜负载) 这种结构是能够更好的match,不过我个人认为取合适的WL更为重要.

取合适的WL是降低random offset,而好的电路结构能降低system offset。这个运放结构在regulator或者bandgap里面应该是比较常用,system offset 相对小。

带宽更大?

提高摆幅!

1. 第一种对称OTA可以提供更高的增益和GBW;2. 镜像比例通常选择3到4,如果只是1的话,就只能起到增加摆幅的作用,太高了会影响稳定性;

3. 第一种OTA有更高SR,可以提高瞬态特性。

另外我觉得你应该改用PMOS输入:两点考虑,噪声和PSR。

赞成

以图2为标准,假设输入和镜像MOS管的偏置电流为ID。

假设图1输入偏置电流为ID/m,输出偏置电流为ID,图1情况下gm * m * ro = sqrt(2k'*W/L*ID/m) * m * [1/(λID)] = sqrt(2k'*W/L*m*ID) *[1/(λID)] ,增益变大了,system offset变小了,SR不变,消耗的电流增加了1/m

假设图1输入偏置电流为ID,输出偏置电流为mID,图1情况下gm * m * ro = sqrt(2k'*W/L*ID) * m * [1/(λ*m*ID)] = sqrt(2k'*W/L*ID) *[1/(λID)] ,增益没变,system offset没变,SR变大了m倍,消耗的电流增加了m倍

假设为两者中间的情况,就是图1输入管的偏置电流<ID,输出偏置电流>ID,这时候增益变大了,system offset变小了,SR变大,消耗的电流增加了。

由于受更多电流源匹配的影响,random offset是增加了,由图2只有一对电流源的奉献变为了图1的三对

gooooooooooooooooooooooood

LDO Gain有个60dB就足够了

如何对提高电源抑制有帮助不太了解,愿详解

不好意思,再看了下结构,发现我错了,特此修正。NMOS作输入时,PSRR+要远大于PSRR-。电源上的噪声通过输出级的上管产生的电流,会被另一条的路径电流所抵消。而地的噪声将直接传递到输出,增益大约为1。

谢谢,非常感谢!

没怎么看懂您说的..m您只指什么? 如果就按图1和图2所示,图一的第一级电流Id=第二级电流Id,SR是怎么得到的图1的更高呢?

m就是图1 PMOS电流镜的比值

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:请教关于一个数模混合仿真的想法

下一篇:哪里有mentor的viewdraw下载?