带隙基准电路受到电源干扰怎么办?

录入:edatop.com 阅读:

有启动电路,基准的瞬态启动特性也正常,想到一个问题,如果电源有较大的扰动或噪声,或有跳动,基准输出会有什么变化,我想知道如何仿真,来验证基准电路抵抗这种干扰的性能?

我试了Vpulse, 用跳变的方波来模拟电源电压的跳动,条件如下:

risetime: 1u,

falltime: 1u,

pulse width: 50u,

period: 100u,

高电平3.5V,低电平2.5V,其中电源电压大于2V以后基准就可以稳定输出约1.2V,按说2.5V~3.5V都在正常工作范围内,但是仿真结果,输出并不是稳定的输出,而是电源电压跟着跳变,下降沿即3.5V变到2.5V时,基准输出变成0.5V。

请教,这是什么原因?这种仿真方法对不对?一般基准仿真不这样仿真吧,是不是每个基准电路都会如此?

我试了Vpulse, 用跳变的方波来模拟电源电压的跳动,条件如下:

risetime: 1u,

falltime: 1u,

pulse width: 50u,

period: 100u,

高电平3.5V,低电平2.5V,其中电源电压大于2V以后基准就可以稳定输出约1.2V,按说2.5V~3.5V都在正常工作范围内,但是仿真结果,输出并不是稳定的输出,而是电源电压跟着跳变,下降沿即3.5V变到2.5V时,基准输出变成0.5V。

请教,这是什么原因?这种仿真方法对不对?一般基准仿真不这样仿真吧,是不是每个基准电路都会如此?

你的跳动有高频成分,估计你BG的高频PSRR比较低,一般分析一下power上可能的噪声源的频率,看一下psrr就OK,BG最重要的是低频PSRR

watch out negative feedback>positive feedback to make sure loop stb!

power上可能的噪声源的频率 怎么分析?

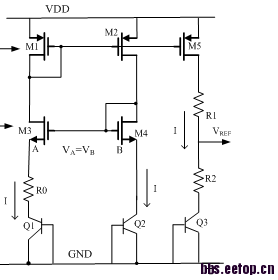

stb怎么仿真?以下面这个基本结构为例

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:encounter中place的问题

下一篇:请教Assura做lvs的问题!